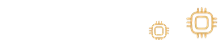

根据《韩国经济日报》的一份报告,三星今年将推出用于高带宽内存 (HBM) 的 3D 封装服务,该报道援引了该公司在圣何塞举行的 2024 年三星晶圆代工论坛上的公告以及“行业消息来源”。HBM 的 3D 封装基本上为 2025 年底至 2026 年的 HBM4 集成铺平了道路,但我们不确定三星今年将封装什么样的内存。对于 3D 封装,三星有一个名为 SAINT(三星高级互连技术)的平台,其中包括三种不同的 3D 堆叠技术:用于 SRAM 的 SAINT-S、用于逻辑芯片的 SAINT-L 和用于 DRAM 堆叠的 SAINT-D,这些堆叠在 CPU 或 GPU 等逻辑芯片之上。该公司多年来一直在研究 SAINT-D(并于 2022 年正式宣布),看起来该技术将在今年的黄金时段做好准备,这将是全球最大的内存制造商的一个里程碑。

根据《韩国经济日报》的一份报告,三星今年将推出用于高带宽内存 (HBM) 的 3D 封装服务,该报道援引了该公司在圣何塞举行的 2024 年三星晶圆代工论坛上的公告以及“行业消息来源”。HBM 的 3D 封装基本上为 2025 年底至 2026 年的 HBM4 集成铺平了道路,但我们不确定三星今年将封装什么样的内存。对于 3D 封装,三星有一个名为 SAINT(三星高级互连技术)的平台,其中包括三种不同的 3D 堆叠技术:用于 SRAM 的 SAINT-S、用于逻辑芯片的 SAINT-L 和用于 DRAM 堆叠的 SAINT-D,这些堆叠在 CPU 或 GPU 等逻辑芯片之上。该公司多年来一直在研究 SAINT-D(并于 2022 年正式宣布),看起来该技术将在今年的黄金时段做好准备,这将是全球最大的内存制造商的一个里程碑。

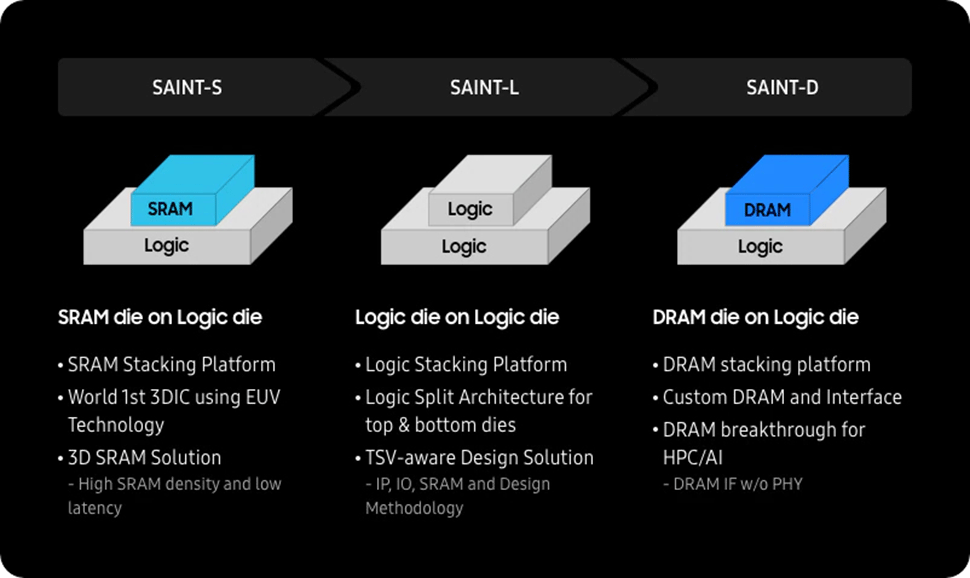

三星的新 3D 封装方法涉及将 HBM 芯片垂直堆叠在处理器顶部,这与现有的 2.5D 技术不同,后者通过硅中介层水平连接 HBM 芯片和 GPU。这种垂直堆叠方法消除了对硅中介层的需求,但需要一个新的 HBM 存储器基模,该芯片使用复杂的工艺技术制造。

3D 封装技术为 HBM 带来了显著的优势,包括更快的数据传输速度、更清晰的信号、更低的功耗和更低的延迟,但封装成本相对较高。三星计划将这种先进的 3D HBM 封装作为交钥匙服务提供,其内存业务部门生产 HBM 芯片,代工部门为无晶圆厂公司组装实际处理器。目前,尚不清楚三星今年会采用SAINT-D技术推出何种芯片产品。将HBM垂直堆叠在逻辑芯片顶部,需要更精细的芯片设计方法,目前,我们还没有获得任何知名处理器公司采用SAINT-D技术封装HBM,并将于 2024 ~2025上半年推出新产品的信息。

展望未来,三星的目标是到 2027 年推出一体化异构集成技术。这项未来的技术将实现两层逻辑芯片的集成,HBM存储器(在内介层上),甚至共封装光学器件(CPO)。

展望未来,三星的目标是到 2027 年推出一体化异构集成技术。这项未来的技术将实现两层逻辑芯片的集成,HBM存储器(在内介层上),甚至共封装光学器件(CPO)。 抗衡台积电台积电、三星和英特尔等领先芯片制造商正在激烈竞争先进封装,这种封装集成了不同的半导体或垂直互连多个芯片。先进的封装允许将多个器件合并封装为单个电子器件。封装技术可以增强芯片性能,而无需通过超精细加工缩小纳米,这在技术上具有挑战性,并且需要更多时间。目前,业界主流是2.5D封装,将芯片尽可能靠近地放置在一起,以减少数据传输瓶颈。全球排名第一的晶圆代工厂台积电凭借其拥有10年历史的2.5D封装技术,成为全球先进封装市场的领导者。台积电正在斥巨资为其客户(包括苹果公司和英伟达)测试和升级其 3D 芯片间堆叠技术 SoIC。全球第三大晶圆代工厂联电 (UMC) 推出了利用硅堆叠技术的晶圆对晶圆 (W2W) 3D IC 项目,为其客户提供尖端解决方案。联电表示,其 W2W 3D IC 项目与 ASE(日月光)、Winbond、Faraday 和 Cadence Design Systems 等公司合作,是一项雄心勃勃的事业,旨在利用 3D 芯片集成技术来满足边缘 AI 应用的特定要求。英特尔使用其下一代 3D 芯片封装技术 Foveros 来制造先进芯片。三星电子自 2021 年推出2.5D 封装技术H-Cube 以来,一直在加速芯片封装技术的发展。三星表示,2.5D 封装技术允许逻辑芯片或高带宽存储器(HBM)以小尺寸堆叠在硅中介层的顶部。消息人士称,借助新的 SAINT 技术,三星旨在提高数据中心和具有设备端 AI 功能的移动 AP 的 AI 芯片的性能。为了追上台积电AI芯片的先进封装,三星电子将推出FO-PLP的2.5D封装技术吸引客户。据悉,三星DS部门先进封装(AVP)团队开始研发将FO-PLP先进封装用于2.5D芯片封装,可将SoC和HBM整合到矽中介层,建构成完整芯片。2.5D封装是近年AI芯片不可或缺的制程。以全球供不应求的英伟达AI芯片来说,就是采2.5D封装技术整合,但由台积电CoWoS 2.5D先进封装拿下订单。与台积电CoWoS 2.5D不同的是,三星FO-PLP 2.5D是在方形基板封装,台积电CoWoS 2.5D是圆形基板,三星FO-PLP 2.5D不会有边缘基板损耗问题,有较高生产率,但因要将芯片由晶圆移植到方形基板,作业程序较复杂。三星战略是利用FO-PLP 2.5D追上台积电,因三星DS部门2019年从三星电机收购FO-PLP后就开始研究智能手表和智能手机处理器商业化,并扩大FO-PLP使用。目前已用于功率半导体器件封装。报道引用韩国市场人士说法,从国际学术会议三星连续发表FO-PLP论文看,三星致力开发FO-PLP,以克服2.5D封装局限性。若FO-PLP成功,就能与晶圆代工和存储器业务互相拉抬,故三星提出一站式方案(Turn-key)吸引客户,为AI芯片设计公司(如英伟达和AMD)生产半导体产品、加上HBM和先进封装。先进封装若更有竞争力,三星就能更壮大半导体业务。

抗衡台积电台积电、三星和英特尔等领先芯片制造商正在激烈竞争先进封装,这种封装集成了不同的半导体或垂直互连多个芯片。先进的封装允许将多个器件合并封装为单个电子器件。封装技术可以增强芯片性能,而无需通过超精细加工缩小纳米,这在技术上具有挑战性,并且需要更多时间。目前,业界主流是2.5D封装,将芯片尽可能靠近地放置在一起,以减少数据传输瓶颈。全球排名第一的晶圆代工厂台积电凭借其拥有10年历史的2.5D封装技术,成为全球先进封装市场的领导者。台积电正在斥巨资为其客户(包括苹果公司和英伟达)测试和升级其 3D 芯片间堆叠技术 SoIC。全球第三大晶圆代工厂联电 (UMC) 推出了利用硅堆叠技术的晶圆对晶圆 (W2W) 3D IC 项目,为其客户提供尖端解决方案。联电表示,其 W2W 3D IC 项目与 ASE(日月光)、Winbond、Faraday 和 Cadence Design Systems 等公司合作,是一项雄心勃勃的事业,旨在利用 3D 芯片集成技术来满足边缘 AI 应用的特定要求。英特尔使用其下一代 3D 芯片封装技术 Foveros 来制造先进芯片。三星电子自 2021 年推出2.5D 封装技术H-Cube 以来,一直在加速芯片封装技术的发展。三星表示,2.5D 封装技术允许逻辑芯片或高带宽存储器(HBM)以小尺寸堆叠在硅中介层的顶部。消息人士称,借助新的 SAINT 技术,三星旨在提高数据中心和具有设备端 AI 功能的移动 AP 的 AI 芯片的性能。为了追上台积电AI芯片的先进封装,三星电子将推出FO-PLP的2.5D封装技术吸引客户。据悉,三星DS部门先进封装(AVP)团队开始研发将FO-PLP先进封装用于2.5D芯片封装,可将SoC和HBM整合到矽中介层,建构成完整芯片。2.5D封装是近年AI芯片不可或缺的制程。以全球供不应求的英伟达AI芯片来说,就是采2.5D封装技术整合,但由台积电CoWoS 2.5D先进封装拿下订单。与台积电CoWoS 2.5D不同的是,三星FO-PLP 2.5D是在方形基板封装,台积电CoWoS 2.5D是圆形基板,三星FO-PLP 2.5D不会有边缘基板损耗问题,有较高生产率,但因要将芯片由晶圆移植到方形基板,作业程序较复杂。三星战略是利用FO-PLP 2.5D追上台积电,因三星DS部门2019年从三星电机收购FO-PLP后就开始研究智能手表和智能手机处理器商业化,并扩大FO-PLP使用。目前已用于功率半导体器件封装。报道引用韩国市场人士说法,从国际学术会议三星连续发表FO-PLP论文看,三星致力开发FO-PLP,以克服2.5D封装局限性。若FO-PLP成功,就能与晶圆代工和存储器业务互相拉抬,故三星提出一站式方案(Turn-key)吸引客户,为AI芯片设计公司(如英伟达和AMD)生产半导体产品、加上HBM和先进封装。先进封装若更有竞争力,三星就能更壮大半导体业务。*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。