来源:内容由半导体行业观察(ID:icbank)编译自imec,谢谢。

在本周举办的2022 年国际电子设备会议 (IEEE IEDM 2022) 上,世界领先的纳米电子和数字技术研究与创新中心 imec 提出了一种半镶嵌(semi-damascene)集成方法,用于实施垂直-水平-垂直 (VHV:vertical-horizontal-vertical) 缩放助推器——旨在启用 4 轨 (4T) 标准单元。半镶嵌工艺使中间线 (MOL) 层的单元边界缩小至 8nm 尖端到尖端 (T2T:tip-to-tip),并提供自对准边缘。设计人员可以使用助推器将标准单元封装得更紧,面积比 5T 设计增加 21%。新颖的路由方案以及半镶嵌集成方法对于逐步将逻辑缩放路线图很好地推进Å时代至关重要。长期以来,提供前端 (FEOL) 和后端 (BEOL) 之间连接的 MOL 一直被组织为单层触点。但目前,它正在扩展到多个层,例如,包括 Mint 和 Vint 层。这些 MOL 层将电信号从晶体管的源极、漏极和栅极传输到局部互连,反之亦然。

Imec 最近推出了一种称为 VHV 的新型标准单元布线架构,其中包括引入额外的 MOL 层 (M0B) 作为缩放助推器,以实现 4T 标准单元设计。有了这个助推器,标准单元中的前三个布线层遵循 VHV 布线方式,而不是 5T 标准单元中的传统 HVH 布线方式。然而,从工艺集成的角度来看,新型两级 MOL VHV 缩放助推器具有挑战性,主要是由于相邻 4T 标准单元之间的边界很紧。单元边界要求相邻的 MOL M0B 线和两个彼此面对的通孔 (VintB) 之间有紧密的 T2T,通孔边缘定义明确——所有这些都在顶部 Mint 层的一个临界尺寸 (CD) 的最小距离内。这意味着对于即将到来的技术节点,T2T 和 VintB 过孔距离需要从 ~24nm 逐渐减少到 ~8nm。这不能再使用直接平版印刷来实现,而是需要自对准图案化策略。

在 IEDM 2022 上,imec 展示了研究人员如何使用涉及直接金属蚀刻的两级半镶嵌方法来定义相邻标准单元之间的紧密边界。,imen纳米互连项目总监兼研究员Zsolt Tőkei说,我们从传统定义的连续线和更宽的过孔开始,一旦完成两个金属层,我们将它们分成两部分,使用顶部 16-18 纳米间距 Mint 层作为最终图案化步骤的硬掩模。这导致 3 个边缘(Mint、VintB 和 M0B)同时自对齐。借助我们的基于 Ru 的两级测试载体,我们获得了 10.5 纳米的平均 via CD 和 8.9 纳米的 M0B T2T——这是一项关键成就。” Imec 研究人员通过线路电阻和隔离特性的初始电气特性来补充结构验证。

Zsolt Tőkei 补充道:“VHV 路由方案是一个关键的扩展助推器,可在 A10、A7、A5、A3 技术节点启用单元边界。” “它还适用于未来的设备架构,例如纳米片、叉片和 CFET。通过将半镶嵌从 BEOL 扩展到 MOL,我们现在还找到了一种集成这种有前途的助推器的方法。然而,还需要进行更详细的调查,为此,imec 正在开发一种新的专用掩模。”

1nm的实现方法探讨

近来,IMEC CMOS 器件技术总监 Naoto Horiguchi 和 imec 研究员兼 imec 纳米互连项目总监 Zsolt Tokei 接受了采访,谈到了他们对1nm等先进工艺实现方式的看法。

沿着扩展路径,他们展示了逻辑器件开发需要如何与在生产线后端引入创新并在越来越大的程度上在生产线中间引入创新齐头并进。

问:您如何看待未来几年逻辑设备的扩展?

Naoto Horiguchi:大多数 IDM 和代工厂最近都宣布从主流 FinFET 过渡到用于其 3nm 或 2nm 逻辑技术世代的环栅 (GAA) 纳米片 FET 架构。imec 的一项发明forksheet 结构则可以延长这种纳米片的生成。在forksheet之后,我们预计互补 FET (CFET) 将进入逻辑扩展路线图。”

“这些转变将使我们能够逐步推动标准单元在 4T 以下的轨道高度缩放,同时仍然提供功率性能优势。

除了 CFET,二硫化钨 (WS 2 )等二维单层晶体材料有望替代 CMOS 沟道中的 Si,为进一步缩小栅极长度提供机会。”

问:这些创新将如何影响BEOL?后端和MOL需要哪些发展才能跟上FEOL的扩展?

Zsolt Tokei:“FEOL)的高级扩展需要与BEOL)的创新齐头并进,这就需要无缝连接到底层设备结构的互连网络。随着 forksheet 架构进入路线图,单元高度被推到 5T 以下,关键 BEOL 层中的金属间距将变得小到 20nm 及以下。从电容、电阻(通孔和导线)以及成本、可印刷性和可靠性的角度来看,这都极具挑战性——需要在设计、模块和材料层面进行创新。这推动了新互连集成方案的发展,例如混合通孔金属化(解决通孔电阻增加)和半镶嵌工艺流程——作为当今主流铜双镶嵌工艺的替代品。半镶嵌涉及金属的直接蚀刻以获得更高纵横比的线条,并且可以包括间隙填充。

Naoto Horiguchi:“为了加强先进逻辑器件缩放和互连开发之间的协同作用,MOL)活动开始发挥越来越重要的作用。将 BEOL 和 FEOL 连接在一起的 MOL 长期以来一直被组织为源极、漏极和栅极的单层接触。

但向低于 5T 电池架构的过渡推动了向多层 MOL 结构的演变,其中添加了额外的层和通孔——类似于过去 BEOL 的演变方式。”

问:您的团队最近取得了哪些突破?

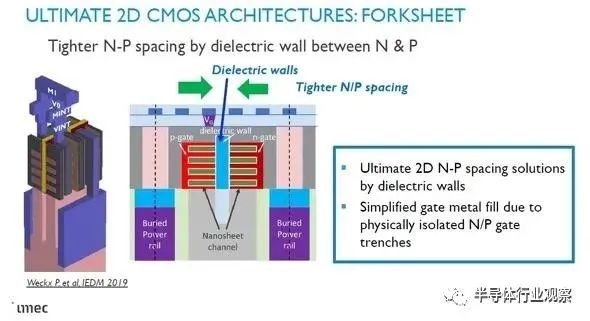

Naoto Horiguchi:“虽然forksheet器件架构的面积和性能优势已经通过 TCAD 模拟显示出来,但我们现在首次展示了功能集成 forksheet的FET 器件的电气特性——这一突破性成果将在 2021 VLSI 上得到强调。我们已经展示了该架构的关键模块,包括介电壁和 17nm np 间距的替代金属栅极图案。尽管forksheet设备是三门设备架构,但在我们的工作中没有观察到静电性能下降。”

问:从纳米互连的角度来看,imec 正在探索哪些途径来补充这一成就?

Zsolt Tokei:forksheet等扩展纳米片架构需要新的 BEOL 集成方案,例如半镶嵌,以实现低于 20 纳米的金属间距。同时,我们正在开发新的多层 MOL 布线方案,例如垂直-水平-垂直 (VHV) 方案。结合缩放增强器(例如自对准触点和埋入式电源轨 (BPR)),这些多层 MOL 方案将为在更小单元高度上实现更高效的单元内布线铺平道路。”

Naoto Horiguchi:“在 MOL 中实施多层工艺流程,结合诸如埋入式电源轨 (BPR) 之类的缩放助推器,这将在很大程度上增强我们基于forksheet的电池设计的可扩展性,将轨道高度从 5T 推到 4T。因此,在 MOL 中引入semi-damascene是 FEOL、MOL 和 BEOL 活动之间cross-fertilization所带来好处的另一个例子。”

问:您期望实现的下一个重要里程碑是什么?

Naoto Horiguchi:“在 forksheet 关键模块和设备演示之后,我们的计划重点将逐渐从 forksheet 转移到 CFET。

CFET 架构由于其许多自由度而很复杂。Imec 将量化功率性能面积 (PPA) 优势和 CFET 工艺流程的复杂性,并向我们的合作伙伴推荐最佳选择。虽然纳米片、forksheet和 CFET 架构将逐渐将单元轨道高度降低到 4T 及以上,但我们正在探索替代器件架构,以解决接触多节距 (CPP) 缩放速度放缓的问题,该接触多节距 (CPP) 测量从一个晶体管的栅极接触到相邻设备上的栅极。”

Zsolt Tokei:“向 1nm CFET 系列逻辑器件的发展推动了新 BEOL 和 MOL 解决方案的开发。在 BEOL 中,我们早些时候提出了一种新的金属化结构,称为“零通孔混合高度”。在这个结构中,每个金属层现在被分成三个独立的子层,这允许根据它们的应用需要调整金属线的高度和纵横比(因此,电容的交换电阻)。

我们很高兴报告第一次 SRAM 评估,确认读取速度(30%)和写入余量(50%)显着提高。目前,我们正在努力实现真正的逻辑单元布局。”

“从长远来看,我们需要通过引入新的导体来补充这些集成方案。感兴趣的是具有比 Ru 或 Mo 更好的品质因数的有序二元或三元化合物。我们已经通过第一次 ab initio 模拟和初步实验开拓了这一领域,现在我们正在与 imec 的材料研发小组密切合作,加强我们的活动。”

问:您希望芯片行业记住的关键信息是什么?

Naoto Horiguchi:“近年来,有一些人声称传统的 CMOS 缩放已经走到了尽头。但是随着许多创新的进行,我们相信我们可以在至少未来十年内继续扩大 CMOS 规模。Imec 是实现这一目标的好地方。与合作伙伴的密切合作帮助我们应对行业最大的挑战,并将逻辑器件扩展到 1nm 技术之外——利用与 imec 的纳米互连、Insite 和材料开发活动的紧密合作。”

Zsolt Tokei:“同样从 BEOL 的角度来看,我们有许多有趣且有效的选择,使我们能够在未来十年解决 RC 延迟瓶颈和流水线互连。我们可以为我们的合作伙伴提供一个全面的路线图,其中包含与未来逻辑器件缩放相关的广泛选项,其中的元素可以重新用于存储器开发。我们正在通过新的见解、改进的集成方案和新材料不断丰富这一路线图——其中一些还将在 7 月份即将举行的 IITC 会议上展示。”

2nm后,晶体管的新选择

从Forksheet到CFET

在2019年的VLSI座谈会上,imec表示将会把CFET应用到5纳米、3纳米、2纳米上,笔者就此向其中一位演讲者提出:“imec计划从哪个技术节点开始使用CFET”?得到了以下回答:“就此,目前imec还没有达成一致意见”。

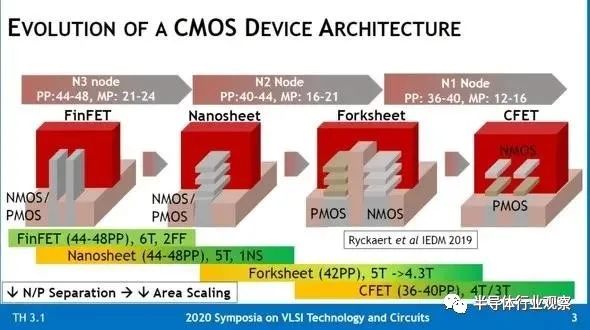

后来,imec在其内部达成了以下共识:3纳米之前采用Nanosheet、2纳米采用Forksheet、1纳米采用CFET。也就是说,在此次VLSI座谈会上,imec的其他发言人,如Sujith Subramanian先生,也是基于以上技术蓝图而做的发表。(如下图)

图一

图一 图2

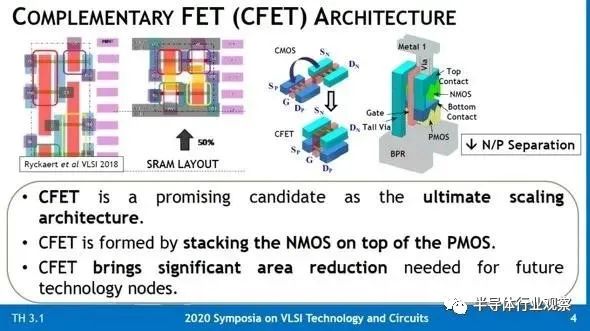

图2此外,在1纳米中,采用了将nMOS和pMOS纵向排列的CFET(如下图8),虽然CFET的工艺流程非常复杂,但毫无疑问,极大地缩小了CMOS、SRAM的面积,达到了集成化。问题是---是否做到了人们所期待的晶体管的特性,这是未来研发的关键。

图3

图31nm以后的晶体管选择:CFET?

在VLSI 2020上,IMEC发表了有关单片CFET的有趣论文,我有机会采访了其中一位作者Airoura Hiroaki。在业界众所周知,FinFET(FF)即将达到其定标寿命。三星已经宣布,他们将在3nm的时候转向水平纳米片(Horizontal Nanosheets :HNS)。台积电(TSMC)保持3nm的FF,但预计将转移到2nm的新架构。

假设英特尔当时仍在追求自己的技术,则预计英特尔将保留7nm的FF,然后再迁移至5nm的HNS。

该行业最可能的路线图是从FF到带有或不带有Forksheets的HNS,然后过渡到CFET(Complimentary FETs),请参见图1。

从以上技术蓝图来看,28纳米使用了High-K/Metal Gate,16纳米---14纳米导入了FinFET,7纳米---5纳米采用了EUV曝光设备,此外,还将Co应用于Middle of Line(MOL)上。

MOL是一种将晶体管(FOEL)与多层配线(BEOL)连接在一起的孔(Via),虽然imec使用了Co,还有其他选择项如Mo、Ru等。

此外,4纳米---3纳米中采用了具有Nanosheet结构的晶体管。

此次的VLSI座谈会上,有关7纳米、5纳米、3纳米的文章发布得比较多,然而,笔者却发现将Gate All Around(GAA)的Nanosheet结构应用在这些节点上的情况是全球共通的认知。

同时从技术蓝图看,在2纳米中,使用搭载了Buried Power Rail(BPR,在晶体管下埋入电源线的构造)的Forksheet晶体管;在1纳米中,将会使用采用了BPR的Complementary FET(CFET)。

imec在其内部达成了以下共识:3纳米之前采用Nanosheet、2纳米采用Forksheet、1纳米采用CFET。

也就是说,在此次VLSI座谈会上,imec也是基于以上技术蓝图而做的发表。从上图可以清晰地看出FinFET、Nanosheet、Forksheet、CFET的结构变化。

从FinFET到CFET,通过将Contact Poly Pitch(PP)做到最小、分离nMOS和pMOS,以达到缩小SRAM面积的效果。

Forksheet 和CFET通过堆叠nFET和pFET器件的CFET改善n到p的间距来缩小尺寸,见图3。

CFET结构在当前的工作中,已经开发了“单片”(monolithic) CFET,方法是将单独的硅片用于nFET和pFET,然后将它们粘合在一起,而按照顺序(sequential),CFET则会将两种类型的FET都制造在同一硅片上。

Imec声称单片技术比顺序技术便宜,而顺序技术要求SOI会增加衬底成本1%。

片CFET的成本优势在1纳米中,IMEC采用了将nMOS和pMOS纵向排列的CFET(如下图8),虽然CFET的工艺流程非常复杂,但毫无疑问,极大地缩小了CMOS、SRAM的面积,达到了集成化。

问题是——是否做到了人们所期待的晶体管的特性,这是未来研发的关键。

我发现起始晶圆成本高出约1%,这有两个原因,一是,我不相信顺序CFET需要SOI,二是,SOI比标准晶圆贵了约1%。整体方法还将需要两个起始晶圆,而不仅仅是一个。

我认为这种成本分析需要更多的调查。在单片方法中,nFET和pFET在分离的晶圆上制造,从而可以针对该器件优化每个器件的制造流程。

随着我们朝N3方向发展,n到p的分离减少了寄生效应并提高了性能。同样,通过从FF移至GAA)可以在所有四个侧面而不是三个侧面上提供一个栅极,从而改善了静电控制。

这项工作中制造的单片CFET为下一代器件提供了顺序CFET的替代方案,需要进一步研究。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。