随着晶体管按比例缩小,它们需要更薄的沟道来实现足够的沟道控制。然而,在硅中,表面粗糙度散射会降低迁移率,从而将最终沟道厚度限制在 3 纳米左右。

二维过渡金属二硫族化物 (TMD:Two-dimensional transition metal dichalcogenides),例如 MoS2和 WSe2,在一定程度上具有吸引力,因为它们避免了这种限制。由于没有平面外悬空键和原子光滑的界面(With no out-of-plane dangling bonds and atomically smooth interfaces),TMD 即使在亚埃厚度下也能避免散射引起的迁移率下降。

尽管如此,TMD 仍代表着硅甚至硅锗现状的根本改变。材料生长、触点形成和器件制造都不同于相应的硅工艺。目前,基础材料研究和器件开发并行进行。在实验室设备中获得良好结果的材料和工艺可能不适合批量生产。

例如,迄今为止大多数 TMD 设备演示都依赖于层转移(layer transfer )技术。这种方法从一个独立的薄膜开始,它可以生长在蓝宝石等兼容基板上,也可以从大块材料上剥离下来。可以使用几种方法中的任何一种将膜转移到可能已经包括底栅结构的准备好的目标衬底。

层转移带来了明显的成本和产量挑战。在 12 月的 IEEE 国际电子器件会议 (IEDM) 上展示的工作中,英特尔的 CJ Dorow 及其同事表明,单栅极 MoS2器件的性能因转移过程而下降。他们在源极和漏极区域观察到 TMD 分层。去掉的低 k 电介质层也在 TMD/氧化物界面留下残留物。半导体晶圆厂更喜欢更“类硅”工艺的灵活性和成本效益,TMD 直接沉积在目标基板上。

一般而言,TMD 生长需要在薄膜质量和最小化沟道厚度的需求之间进行权衡。原子级沉积 (ALD) 电介质和通过化学气相沉积 (CVD) 生长的 TMD 都容易出现针孔和其他缺陷。尽管如此,在 12 月的 IEEE IEDM 上发表的几篇论文表明,该行业正在朝着直接沉积 TMD 的方向取得进展。例如,北京大学的 Xinhang Shi 及其同事使用低压 CVD直接在 SiO2上生长 WSe2双层。非常高的温度过程 (890°C) 使器件具有425 μA/μm 的创纪录高 Ids。薄膜特性与氧化物厚度无关。或者,台积电的 Yun-Yan Chung 及其同事使用钨垫作为 WS2生长的种子层,构建具有两个和三个堆叠沟道的设备

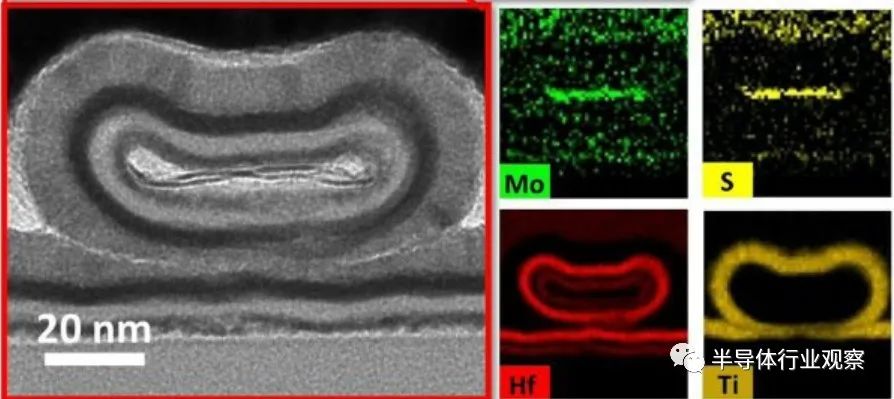

图 1:完全被栅极堆叠包围的单层 MoS2 纳米片的 TEM 横截面。较小的图像显示 EDX 元素映射。

用于掺杂和阈值电压控制的电介质

完整的 CMOS 工艺不仅仅是简单地沉积沟道材料。该过程还必须促进空穴和电子传导。在 TMD 中,掺杂、电介质沉积和 Vth Tuning彼此密不可分。由于目前不可能对半导体本身进行掺杂,因此器件依靠覆盖层来调节传导并提供 nFET 或 pFET 行为。即使确定了合适的材料,TMD 表面的二维特征也会使覆盖层沉积复杂化。除了晶界和其他缺陷外,沉积氧化物的潜在成核位置非常少。

WSe2是一种双极性材料,这意味着费米能级在施加电场的情况下在价带和导带之间移动。因此,相同的材料可以传导电子或空穴

台积电的几个不同小组一直在从不同角度研究WSe2传导和掺杂。一组使用氧等离子体将WSe2半导体单层转化为Ox。该过程是自限性的,不影响底层的WSe2材料,最终的掺杂水平取决于起始材料中的层间耦合。较厚的起始材料具有较高的价带边缘,从而在转化为氧化物后导致更高的掺杂。在 Ang-Sheng Chou 介绍的工作中,另一个 TSMC 小组将 MoO x盖层用于 pFET 器件和 SiON x对于 nFET 器件。连同下面讨论的新颖接触技术,这些覆盖层提供了一些迄今为止最好的 TMD 晶体管结果。

在普渡大学,研究人员使用六方氮化硼 (hBN:hexagonal boron nitride) 作为界面层以促进电介质沉积。他们的工作强调了“缺陷”(defects)和“陷阱”(traps)之间的区别。正如他们所解释的那样,缺陷既可能发生在电介质体内部,也可能发生在电介质——半导体界面处。然而,只有当费米能级穿过缺陷能带时,缺陷才会变成陷阱。在 hBN 中封装单层 MoS2降低了亚阈值摆动并增加了V th,这意味着界面陷阱被消除或停用。hBN 层似乎可以阻挡 TMD 薄膜上的吸收物,这是电荷陷阱的潜在来源。

不幸的是,hBN 本身并不是一种合适的电介质。它也是一种类石墨材料,具有弱的面外键合,使得直接在 hBN 上生长电介质具有挑战性。Purdue 小组使用钽种子层进行电介质沉积。相对于更常见的铝种子,他们发现亚阈值摆幅退化较少,V th偏移也减少。

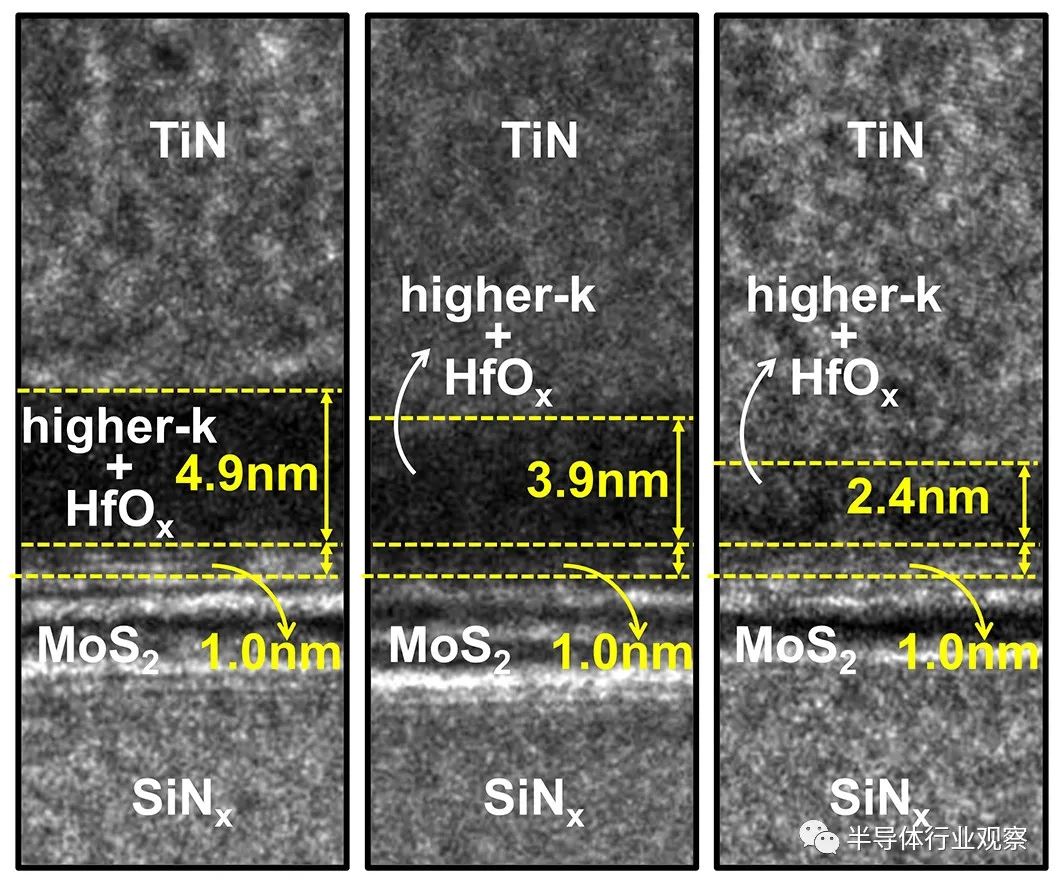

图 2:通过系统地分析关键工艺参数,TSMC 的研究人员将铪基电介质与CVD生长的 MoS2集成在一起,构建了EOT ~1nm和近乎理想的亚阈值摆动的顶栅 nFET。这项工作特别值得注意,因为在 TMD 上沉积无针孔电介质是出了名的困难。

堆叠沟道和接触

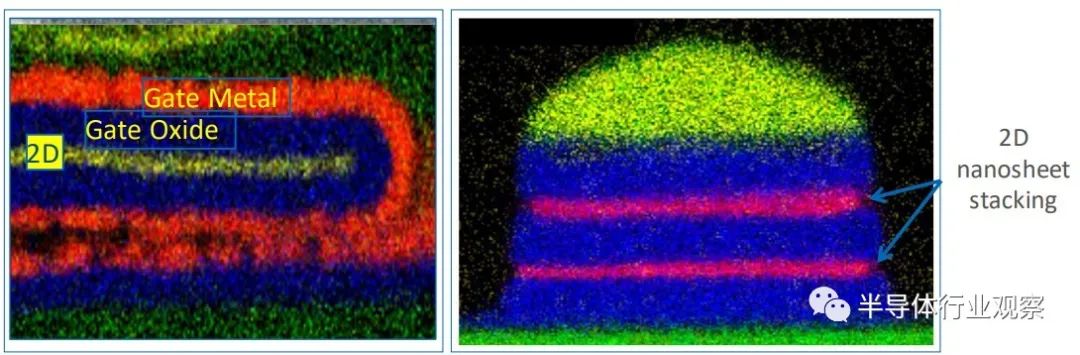

由于需要堆叠沟道,实际设备可能会看到更复杂的工艺。单个 TMD 单层不能承载与硅纳米片一样多的电流,因此设备将需要多个堆叠的 TMD 片。与堆叠的硅纳米片一样,最小化片之间的间距可以减少寄生电容。

图3:二维MoS2堆叠纳米带结构。

由于 TMD 层非常薄,Yun-Yan Chung 的团队指出机械稳定性也是一个问题。他们使用牺牲电介质来提高刚度并防止制造过程中下垂。内部垫片和金属触点有助于将沟道固定在成品设备中。

自从这些器件被提出以来,TMD 晶体管构造的最后一步,即与电路的其余部分接触,就受到了广泛的研究关注。尽管如此,接触电阻和间隔电阻仍占二维晶体管总器件电阻的 80%,比硅接触电阻和间隔电阻的贡献要大得多。最近使用铋和锑等半金属的研究为 nFET 提供了良好的结果,但 pFET 触点仍然是一个未解决的问题。

正如 Ang-Sheng Chou 的团队所解释的那样,大多数提议的接触都有一个不幸的空穴传导能带排列。他们的工作利用了 WSe2的双极性特性,将单一的锑/铂堆栈用于 nFET 和 pFET 器件。锑(Sb,功函数 4.4 eV)提供缓冲层,最大限度地减少对底层半导体的损坏。铂(Pt,功函数 5.6 eV)调节功函数。两种材料的比例可调,以实现 nFET 和 pFET 所需的功函数。最后,他们报告了电子和空穴的低势垒高度、低接触电阻和约 150 μA/μm 的导通电流。

二维半导体的下一步是什么?

与结果本身相比,来自英特尔和台积电等公司的大量报告表明,基于 TMD 的晶体管是接替硅的重要候选者。虽然在过去几年中,该行业已经开始阐明此类设备的潜在设计——MoS 2或 WSe 2沟道,具有半金属接触——稳健的、可制造的制造工艺尚未出现。

来源:半导体行业观察

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。