二维半导体有机会激发电子设备功能的重大进步,取代硅基芯片。然而,许多问题继续阻碍这些设备的发展。一个主要问题是载流子迁移率,即电子在半导体中的移动速度。这些 2D 半导体在这一领域的速度非常慢,限制了改进和实际应用的能力。

德克萨斯大学奥斯汀分校的研究人员发现了十多种不同的二维半导体材料,这些材料可以让电子快速四处移动,从而为电子产品的能力飞跃打开了大门。

“如果你能用二维半导体代替硅,这将导致更快的设备消耗更少的能量,”领导该项目的科克雷尔工程学院沃克机械工程系和德克萨斯材料研究所助理教授 Yuanyue Liu 说。

传统的硅基半导体和二维半导体之间的最大区别在于它们的几何形状。二维半导体要薄得多,只有几个原子层厚。这在许多方面都是有利的,因为使半导体更小的推动力不断增强。

2D 半导体的紧凑性也会产生问题。电子被紧紧地包裹着,没有太多的自由移动。在这些较小的空间中,散射源更容易使它们偏离轨道,这就是为什么二维半导体中的载流子迁移率通常较低,从而阻碍了功率和效率的提高。

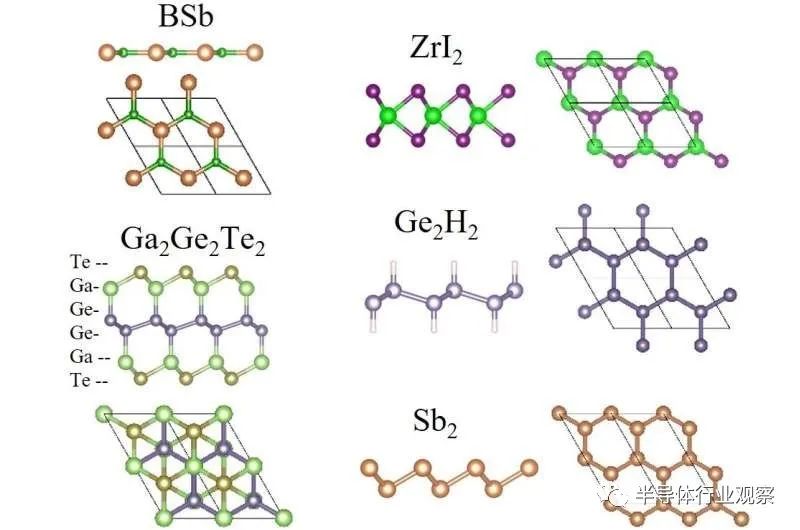

研究人员发现的 14 种载流子迁移率高的材料是这个问题的一个例外。这些材料的独特特性使电子更加透明,使它们基本上不可见于散射,并使电子保持在轨道上。为了找到这些材料,研究人员使用了现有的材料数据库和他们假设会提高机动性的特征清单。然后他们使用量子力学方法准确计算材料中的载流子迁移率。

“我们在数千种材料中只发现了 14 种具有潜在高载流子迁移率的材料,这一事实并不与传统智慧相矛盾,”刘说。“这表明找到具有高载流子迁移率的二维半导体是多么困难。”Liu说,下一步是与实验研究人员合作,并致力于制造材料以测试和验证他们的发现。尽管 Liu 对这些发现充满信心,但他警告说,它们仍然是理论上的,需要通过现实世界的测试来证实。

该项目的其他团队成员包括来自沃克机械工程系和德州材料研究所的 Chenmu Zhang、Ruoyu Wang 和 Himani Mishra。

硅的时代终于要结束了,这会是最优继任者?

将二维材料集成到传统的半导体制造工艺中可能是芯片行业历史上更激进的变化之一。

虽然在半导体制造中引入任何新材料都会带来痛苦和痛苦,但过渡金属二硫化物 (TMD:transition metal dichalcogenides) 支持各种新的器件概念,包括BEOL晶体管和单晶体管逻辑栅极。新的背栅(back-gate)和分栅(split-gate)晶体管已经显示出二维设计的前景。

一段时间以来,人们已经了解了诸如 MoS 2和 WS 2等 TMD 对晶体管沟道的优势。随着器件的缩小,沟道厚度也需要缩小,以最大限度地减少短沟道效应。然而,在硅中,非常薄的层会受到载流子迁移率降低的影响。陷阱和其他界面缺陷的影响压倒了体积特性。

相比之下,二维材料没有平面外悬挂键(out-of-plane dangling bonds),从而减少或消除了界面效应。虽然业界一致认为 3nm 是硅沟道的实际厚度限制,但 MoS 2单层的厚度小于 1nm。

直到最近,接触电阻还是采用 TMD 的最大障碍。然而,在过去一年左右的时间里,锑和铋等半金属(semimetals)已成为潜在的解决方案。半金属往往不会在半导体带隙中产生电子态,因为它们本身没有带隙,而且它们在费米能级上的态密度很低。

尽管如此,将 TMD 与现有的半导体制造基础设施集成仍然具有挑战性。所涉及的许多材料——钼、硫、锑和铋等——对行业来说都是新的,可能对现有工艺造成损害。

制造 TMD 单层

最好的 TMD 单层是通过从块状材料上剥离或在蓝宝石上进行分子束外延制造的,这两种方法都需要随后转移到传统晶圆上。虽然它是一种对制造更友好的工艺,但金属有机化学气相沉积需要非常高的沉积温度,并且可以将碳副产物掺入沉积膜中。

在早前的 VLSI 技术研讨会上,英特尔的组件研究工程师 Kirby Maxey 和他的同事指出,实际上 TMD 晶体管有两种不同的用例。一种是在生产线前端,它使用 TMD 代替高性能 finFET 或硅纳米片晶体管。该应用依赖于高质量的单晶单层,此时需要在 1,000°C 附近的沉积温度。英特尔小组表明,金属有机前体物质的热解会导致碳沉积以及 TMD,但替代前体和优化的工艺条件可以提高薄膜质量。

第二个潜在用例将 TMD 放置在第二(或第三)有源层中,与中间金属和接触层垂直堆叠。一旦金属层在晶圆上,沉积温度就会受到更多限制。但是这些后端晶体管可能更大,并且能够使用更厚的多晶沟道。成功的沉积工艺需要与沉积发生时晶圆上的任何材料兼容。

高度缩放的 FEOL 设备寻求最小化沟道厚度,仅使用单层 TMD 材料。在第二层开始生长之前,第一个成核位点应该合并成一个连续的薄膜。在今年的材料研究学会春季会议上,亚琛工业大学的研究员 Songyao Tang 及其同事分析了 WS 2单分子层的生长和聚结。随着初始的nucleation islands变大,他们发现中心到边缘的距离超过了吸附原子的迁移距离。当吸附原子无法到达微晶的边缘时,就会形成双层。通常,过早的双层可以覆盖薄膜总表面积的 30%。

亚琛工业大学小组确定了几种减少双层形成的方法。如果每个单独的微晶都更小,那么吸附原子就不需要走那么远就能到达边缘。因此,一种可能的解决方案是减小晶粒尺寸,同时增加成核位置的数量。英特尔小组将这一想法更进一步,使用过渡金属氧化物模式作为与硫属元素前体反应的模板。使用模板,工艺工程师可以控制 TMD 晶粒相对于预期电路图案的位置和方向。

较高的沉积温度通过增加吸附原子在结合到生长膜中之前可以迁移的距离来减少双层形成。不过,TMD 沉积温度已经相当高,制造商希望降低它们。最后,降低生长速率使每个吸附原子有更多时间在被随后的生长掩埋之前找到一个能量有利的位置。

新器件设计支持新逻辑概念

随着提议的器件设计走向制造,工艺工程师必须确定是否存在合理的集成方案。例如,许多提议的设计依赖于back gate,要么应用一般的反向偏置,要么形成单独控制的局部栅极。虽然这样的设计相对容易通过层转移技术制造,但直接在预先存在的栅极电介质上生长高质量的 TMD 材料并不那么简单。

图 1:具有可以强烈累积的厚而均匀的 EOT,全背栅配置产生最高的离子 (a);顶栅+FBG有不同的EOT,单独扫过;本地背栅 (c) 和连接的双栅 (d) 提供了 EOT 扩展的好处。资料来源:IMEC

在 12 月的 IEEE 电子设备会议上展示的工作中,Imec 的研究员 Quentin Smets 及其同事提出了四种不同的设计——仅全背栅、顶栅加全背栅设计、仅局部背栅和顶栅加局部背栅设计栅极“连接双栅极”设计。其中,连接的双栅极设计提供了最好的沟道控制,但结果不太一致。局部背栅处理导致沟道中的形貌。在最短的栅极长度处,顶部栅极电极和电介质之间存在间隙,这可能是由于蚀刻不完全。这些不太理想的结果增加了可变性并为工艺改进提供了机会,但 CDG 设计仍然提供始终如一的更好性能。

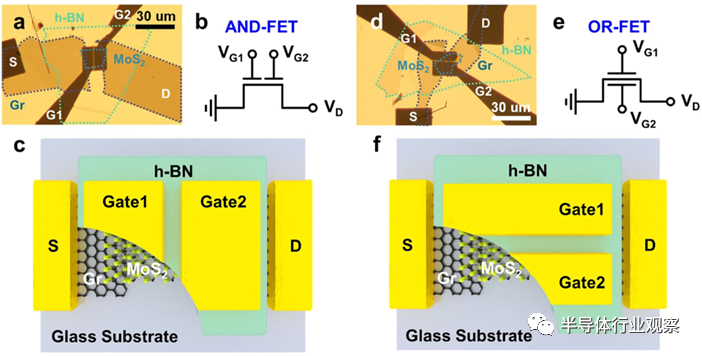

在硅栅环设计中,整个栅极在电气上是一个单一的单元。只有一个偏置旋钮。使用双独立栅极,有两个。具有两个输入信号和一个输出信号的器件可能定义一个单晶体管逻辑栅极。传统的栅极需要至少两个晶体管。相比之下,单晶体管栅极在更小的电路占位面积内提供相同的功能。台积电的 Yun-Yan Chung 及其同事于 2020 年首次提出了基于独立控制的顶栅和底栅的单晶体管栅极。最近,韩国仁荷大学的 Minjong Lee 及其同事展示了带有分离顶栅的设备。在他们的 AND-FET 晶体管/栅极中,栅极的两半垂直于沟道。仅当栅极的两半都“开启”时,晶体管才“开启”。或者,在 OR-FET 晶体管/栅极中,栅极的一半与沟道平行。如果栅极的任何一半“开启”,则晶体管“开启”。

纵向和横向Split-Gate 模型

图 2:AND-FET(a、b、c)和 OR-FET(d、e、f)的图像、电路图和 3D 示意俯视图。资料来源:知识共享

结论

现在说基于过渡金属二硫化物沟道的单晶体管栅极是否是数字逻辑的未来,或者晶体管最终是否会进入 BEOL 堆栈还为时过早。但随着硅的终结——这一次可能是真的——这些材料提供了一种对后硅未来的看法。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。