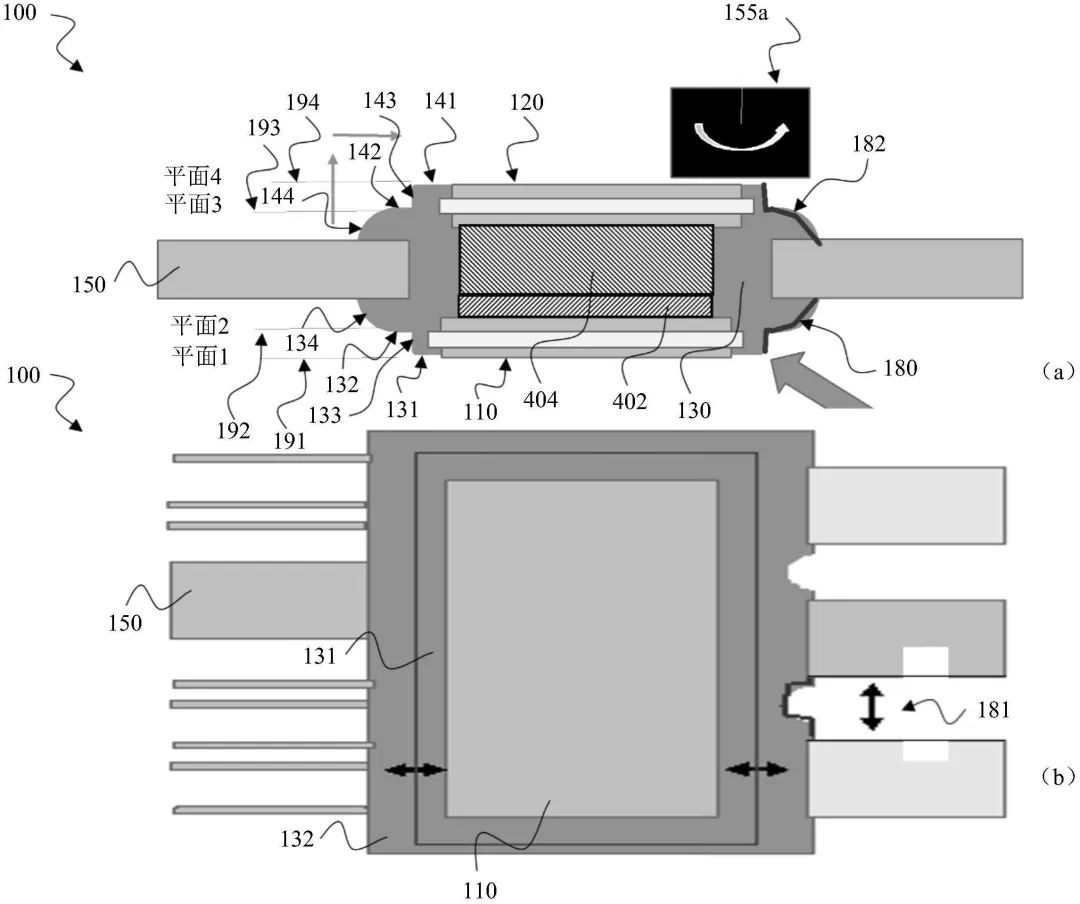

天眼查显示,华为技术有限公司“半导体封装”专利公布,申请公布日为10月31日,申请公布号为CN116982152A。

专利摘要显示,本公开涉及一种半导体封装,该半导体封装包括:第一衬底、半导体芯片、引线框和密封剂。

专利摘要显示,本公开涉及一种半导体封装,该半导体封装包括:第一衬底、半导体芯片、引线框和密封剂。该密封剂的下主面包括在第一平面中延伸的第一部分、在第二平面中延伸的第二部分、在该第一平面与该第二平面之间的第一过渡区中延伸的第三部分,以及在该第二平面与至少一个引线之间的第二过渡区中延伸的第四部分。该密封剂的该第一部分和该第一衬底的下主面在相同的第一平面中延伸,该第一平面形成该封装的下散热表面。该密封剂的该第二部分、该第三部分和该第四部分的尺寸被设置为在该密封剂的该第一部分与该至少一个引线之间保持第一预定义最小距离。

概念解析:

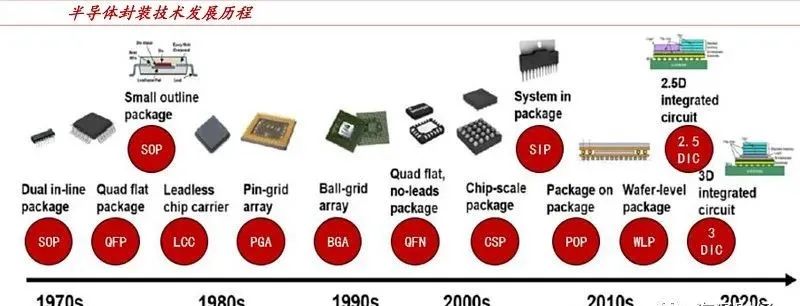

先进封装是指前沿的倒装芯片封装(FC,Flip chip)、晶圆级封装(WLP,Wafer level packaging)、系统级封装(SiP, System In a Package)和2.5D、3D封装等,作为提高连接密度、提高系统集成度与小型化的重要方法。

封装是指将生产加工后的晶圆进行切割、焊线塑封,使电路与外部器件实现连接,并为半导体产品提供机械保护,使其免受物理、化学等环境因素损失的工艺。先进封装采用了先进的设计思路和先进的集成工艺,对芯片进行封装级重构,并且能有效提高系统功能密度的封装技术。

先进封装的四要素是指:RDL,TSV,Bump, Wafer,任何一款封装,如果具备了四要素中的任意一个,都可以称之为先进封装。在先进封装的四要素中,RDL起着XY平面电气延伸的作用,TSV起着Z轴电气延伸的作用,Bump起着界面互联和应力缓冲的作用,Wafer则作为集成电路的载体以及RDL和介质和载体

半导体封装技术由传统到先进共经历了四个发展历程:通孔插装时代、表面贴装时代、面积阵列封装时代和先进封装时代,先进封装技术是延续摩尔定律的最佳选择,在不提高半导体芯片制程的情况下能够进一步提高集成度,显现终端产品轻薄短小等效果。

先进封装发展增大封装设备需求。先进封装中,芯片层数增加,芯片厚度需要更加轻薄以减小体积,因此减薄设备需求增加;ChipLET中,芯片变小且数量变多,划片时需要将晶圆切割为更多小芯片,先进封装中划片机需求的数量和精度都会提升;芯片变小且数量提高之后,对固晶机的需求量和精度要求都会提升。

1.Bump (凸块)工艺与设备

凸块是定向指生长于芯片表面,与芯片焊盘直接或间接相连的具有金属导电特性的突起物。凸块是芯片倒装必备工艺,是先进封装的核心技术之一。

1)凸块可分为金凸块、铜镍金凸块、铜柱凸块、焊球凸块

金凸块主要应用于显示驱动芯片、传感器、电子标签等产品封装;铜镍金凸块主要应用于电源管理等大电流、需低阻抗的芯片封装;铜柱凸块主要应用于通用处理器、图像处理器、存储器芯片、ASIC、FPGA、电源管理芯片、射频前端芯片、基带芯片、功率放大器、汽车电子等产品或领域;锡凸块主要应用于图像传感器、电源管理芯片、高速器件、光电器件等领域。

2)凸块工艺所需设备各不相同

金/铜凸块工艺:

1)采用溅射或其他物理气相沉积的方式再晶圆表面沉积一层 Ti/Cu 等金属作为电镀的种子层;

2)在晶圆表面涂一定厚度的光刻胶,并运用光刻曝光工艺形成所需要图形;

3)对晶圆进行电镀,通过控制电镀电流大小、电镀时间等,从光刻胶开窗图形底部生长并得到一定厚度的金属层;

4)去除多余光刻胶。

锡凸块工艺 :

与铜柱凸块流程相似,凸块结构主要由铜焊盘和锡帽构成,差别主要在于焊盘的高度较低,同时锡帽合金是成品锡球通过钢板印刷,在助焊剂以及氮气环境下高温熔融回流与铜焊盘形成的整体产物。锡凸块一般是铜柱凸块尺寸的 3~5 倍,球体较大,可焊性更强。

铜镍金凸块工艺:

采用晶圆凸块的基本制造流程,电镀厚度超过 10μm以上的铜镍金凸块。新凸块替代了芯片的部分线路结构,优化了 I/O 设计,大幅降低了导通电阻。

2.TSV (硅通孔)工艺与设备

TSV (Through Silicon Via)即硅通孔技术,是一种利用垂直硅通孔实现芯片互连的方法,相比于传统引线连接,具有更短的连接距离、更高的机械强度、更薄的芯片厚度、更高的封装密度,同时还可以实现异种芯片的互连。

TSV 的制作工艺流程为在硅片上刻蚀通孔,侧壁沉积金属粘附层、阻挡层和种子层,TSV 通孔中电镀铜金属作为导体,使用化学机械抛光(CMP)将硅片减薄,最后叠层键合。

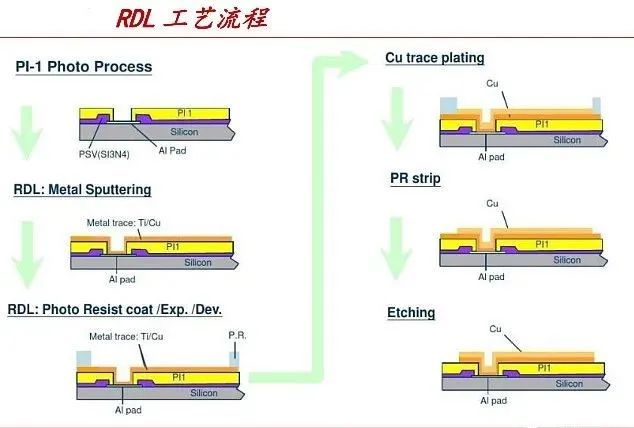

3.RDL(再布线)工艺与设备

RDL (ReDistribution Layer,重布线层是实现芯片水平方向互连的关键技术,可将芯片上原来设计的 I/O 焊盘位臵通过晶圆级金属布线工艺变换位臵和排列,形成新的互连结构。

RDL 需要的设备包括曝光设备、PVD 设备等。RDL 的工艺流程:1)形成钝化绝缘层并开口;2)沉积粘附层和种子层;3)光刻显影形成线路图案并电镀填充;4)去除光刻胶并刻蚀粘附层和种子层;5)重复上述步骤进行下一层的 RDL 布线。

华为封装新专利对麒麟的解决方案

对于麒麟9000s的量产,国内和国外从发售之日起,便不停的研究,最终也没得出什么结果。但拆机结果有两点:

第一,麒麟9000s比麒麟9000大了一圈

第二,麒麟9000s散热方面做了特殊结构

这两点与华为这份封装专利不谋而合,尤其是散热方面,专利里有详细介绍与解决方案。

这份专利较为新颖,相较于其他工艺,绝缘、散热、引线增量较多。

当前国内龙头封测厂商均有50%以上收入来自先进封装业务,在先进封装技术实现持续突破:

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。