HBM俨然成为了当前存储行业竞争中最为鲜美的一块蛋糕。近日,台积电宣布结合N12FFC+和N5制程技术,生产用于HBM4的基础裸片,为HBM 4做好扩产准备,并且CoWoS先进封装产能多次扩产,只为满足行业高涨的HBM需求。三大存储原厂也动态不断,此前SK海力士、三星、美光均表示近两年HBM产能已售罄,近期,三星和SK海力士两家表示为了满足需求,他们将超过20%的DRAM产线转换为HBM产线。随着HBM3E和HBM4的持续推进,带动行业生态发生变革,三大存储原厂与台积电比以往更加紧密的联系在一起。

01

概述

1.HBM

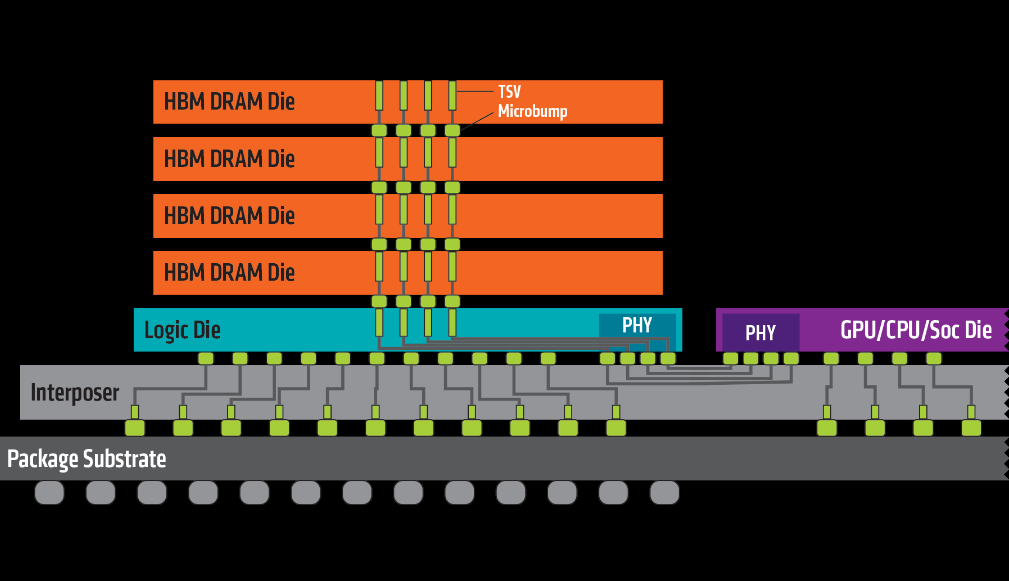

图片来源:AMD

如上图所示,HBM是由多个DRAM堆叠而成,主要利用TSV(硅通孔)和微凸块(Micro bump)将裸片相连接,多层DRAM die再与最下层的Base die连接,然后通过凸块(Bump)与硅中阶层(interposer)互联。同一平面内,HBM与GPU、CPU或ASIC共同铺设在硅中阶层上,再通过CoWoS等2.5D先进封装工艺相互连接,硅中介层通过CuBump连接至封装基板上,最后封装基板再通过锡球与下方PCB基板相连。该产品巧妙的设计大大缩小了尺寸面积,容量扩大的同时,实现了高带宽、低延迟、低功耗的效果。

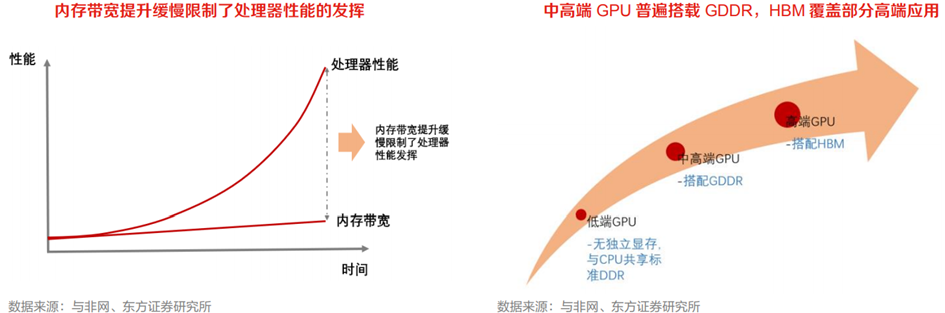

AI时代随着计算需求的不断提升,高端GPU、存储器等需求供不应求。当前GPU补位CPU功能,并不断强化自身算力。但是处理器的性能以每年大约55%速度快速提升,而内存性能的提升速度则只有每年10%左右。目前传统显存GDDR5等也面临着带宽低、功耗高等瓶颈,GPUCPU也算不过来了。

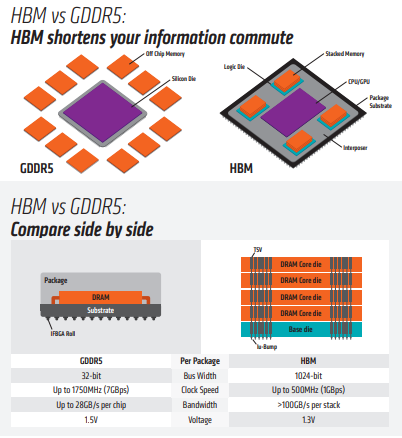

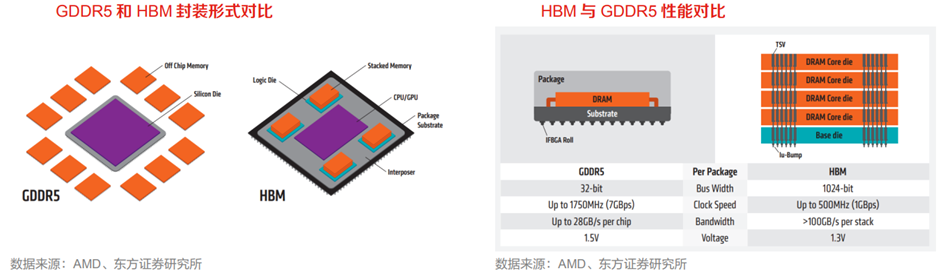

GPU显存一般采用GDDR或者HBM两种方案,但行业多数据显示,HBM性能远超GDDR。此处来看看AMD关于HBM与DDR(Double Data Rate)内存的参数对比,以业界最为火爆的GDDR5为例。

图片来源:AMD

根据AMD数据,从显存位宽来看,GDDR5为32-bit,HBM为其四倍,达到了1024-bit;从时钟频率来看,HBM为500MHz,远远小于GDDR5的1750MHz;从显存带宽来看,HBM的一个stack大于100GB/s,而GDDR5的一颗芯片为25GB/s。在数据传输速率上,HBM远高于GDDR5。而从空间利用角度来看,HBM由于与GPU封装在一块,从而大幅度减少了显卡PCB的空间,而GDDR5芯片面积为HBM芯片三倍,这意味着HBM能够在更小的空间内,实现更大的容量。因此,HBM可以在实现高带宽和高容量的同时节约芯片面积和功耗,被视为GPU存储单元理想解决方案。

但是HBM对比GDDR5/DDR5等依旧存在一定劣势。TrendForce集邦咨询研究显示,在相同制程及容量下,HBM颗粒尺寸较DDR5大35%~45%;良率(包含TSV封装良率),则比起DDR5低约20%~30%;生产周期(包含TSV)较DDR5多1.5-2个月,整体从投片到产出与封装完成需要两个季度以上。从长远发展角度看,在AI浪潮之下,业界大厂率先考虑抢夺HBM就变得十分合理了。

据TrendForce集邦咨询最新研究,三大原厂开始提高先进制程的投片,继存储器合约价翻扬后,公司资金投入开始增加,产能提升将集中在今年下半年,预期1alpha nm(含)以上投片至年底将占DRAM总投片比重约40%。其中,HBM由于获利表现佳,加上需求持续看增,故生产顺序最优先。但受限于良率仅约50~60%,且晶圆面积相较DRAM产品,放大逾60%,意即所占投片比重高。以各家TSV产能来看,至年底HBM将占先进制程比重35%,其余则用以生产LPDDR5(X)与DDR5产品。

目前HBM已然成为AI服务器、数据中心、汽车驾驶等高性能计算领域的标配,未来其适用市场还在不断拓宽。据TrendForce集邦咨询研究显示,产能方面,2023~2024年HBM占DRAM总产能分别是2%及5%,至2025年占比预估将超过10%。产值方面,2024年起HBM之于DRAM总产值预估可逾20%,至2025年占比有机会逾三成。展望2025年,由主要AI解决方案供应商的角度来看,HBM规格需求大幅转向HBM3e,且将会有更多12hi的产品出现,带动单芯片搭载HBM的容量提升。2024年的HBM需求位元年成长率近200%,2025年可望将再翻倍。

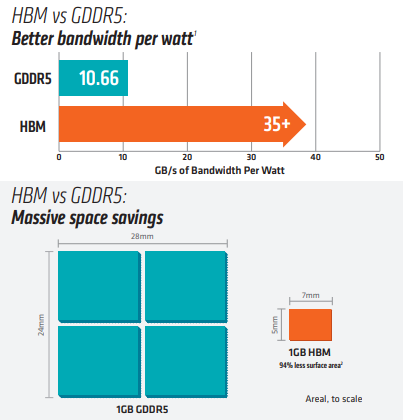

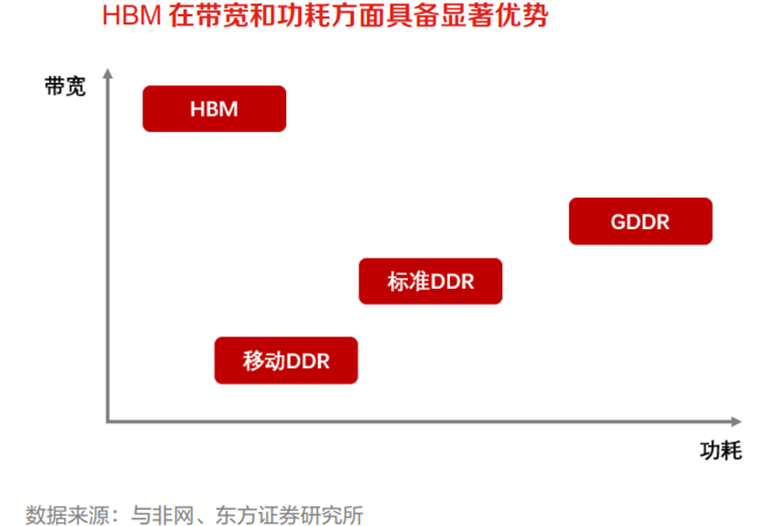

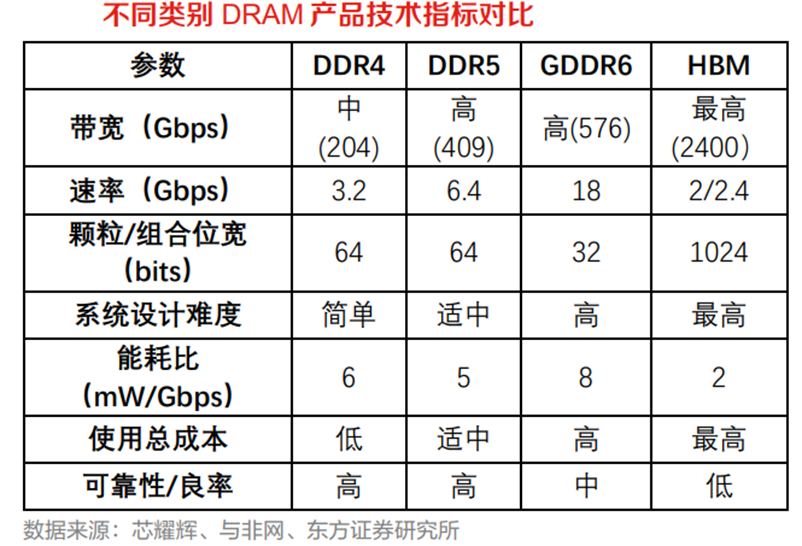

2.优势

HBM在带宽、功耗、封装体积方面具备明显优势。按照不同应用场景,行业标准组织JEDEC将DRAM分为三个类型:标准DDR、移动DDR以及图形DDR,图形DDR中包括GDDR和HBM。相比于标准的DDR4、DDR5等产品,以GDDR和HBM为代表的图形DDR具备更高的带宽,其中HBM在实现更大带宽的同时也具备更小的功耗和封装尺寸。

GDDR和HBM有效解决了内存墙的问题,在中高端GPU中得到广泛应用。过去20年中,处理器的峰值计算能力增加了90,000倍,但是内存/硬件互连带宽却只是提高了30倍。存储性能的提升远远跟不上处理器性能提升,导致内存性能极大限制了处理器性能的发挥,对指令和数据的搬运(写入和读出)的时间将是处理器运算所消耗时间的几十倍乃至几百倍,而且引发了高能耗,即出现了“内存墙”问题。具备更高带宽的GDDR和HBM相比传统DDR有更高的带宽,因此有效的解决了该问题,GDDR和成为中高端GPU搭载的主流内存方案,HBM也在部分高端GPU中得到应用。

3.HBM有望替代GDDR成为主流方案

AI大模型对于数据传输提出了更高的要求,HBM有望替代GDDR成为主流方案:

GDDR5功耗更高,高功耗未来会限制GPU的性能提升;GDDR5为了实现更高带宽,需要电路承载更大的电压,导致电路尺寸偏大。NAND、DRAM和Optics等技术将受益于片上集成,但在技术上并不兼容。

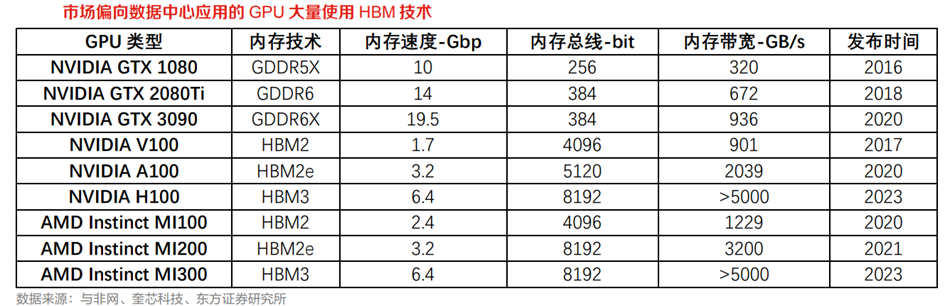

主流数据中心GPU均采用HBM技术。英伟达V100、A100、H100均采用HBM内存,同样,AMDMI100、MI200、MI300也都采用HBM内存,目前HBM内存在数据中心GPU中逐步占据主导地位。

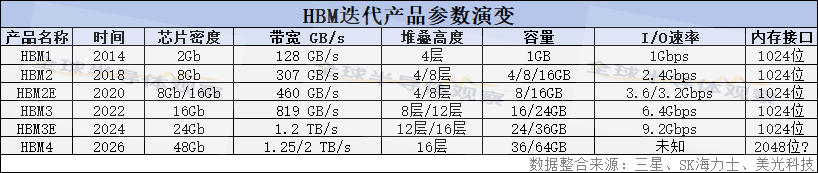

4.HBM持续迭代,带宽、速率提升

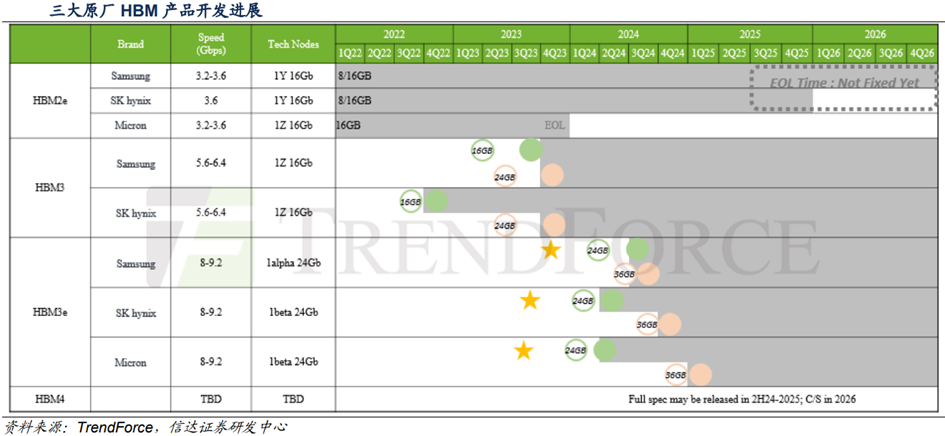

自2013年SK海力士推出第一代HBM以来,在三大原厂的竞合下,至今已历经第二代(HBM2)、第三代(HBM2E)、第四代(HBM3)、第五代(HBM3E)产品。

今年HBM3e将是市场主流,集中在今年下半年出货。另外据行业消息,第六代(HBM4)也正在研发中,变革较大,一改一代至五代的1024位内存接口,集中采用2048位内存接口,有望使传输速度再次翻倍。今天我们的关注焦点也将集中在HBM3E及HBM4上。

其一,「HBM3进阶到HBM3e」,预期NVIDIA将于今年下半年开始扩大出货搭载HBM3e的H200,取代H100成为主流,随后GB200及B100等亦将采用HBM3e。AMD则规划年底前推出MI350新品,期间可能尝试先推MI32x等过渡型产品,与H200相抗衡,均采HBM3e。

其二,「HBM搭载容量持续扩增」,为了提升AI服务器整体运算效能及系统频宽,将由目前市场主要采用的NVIDIA H100(80GB),至2024年底后将提升往192~288GB容量发展;AMD亦从原MI300A仅搭载128GB,GPU新品搭载HBM容量亦将达288GB。

其三,「搭载HBM3e的GPU产品线,将从8hi往12hi发展」,NVIDIA的B100、GB200主要搭载8hi HBM3e,达192GB,2025年则将推出B200,搭载12hi HBM3e,达288GB;AMD将于今年底推出的MI350或2025年推出的MI375系列,预计均会搭载12hi HBM3e,达288G。

相较于普通存储芯片,HBM芯片价格相对较高,且有继续上升趋势。TrendForce集邦咨询表示,HBM3e的TSV良率目前仅约40~60%,仍有待提升,加上并非三大原厂都已经通过HBM3e的客户验证,故HBM买方也愿意接受涨价,以锁定质量稳定的货源。并且未来HBM每Gb单价可能因DRAM供应商的可靠度,以及供应能力产生价差,对于供应商而言,未来平均销售单价将会因此出现差异,并进一步影响获利。

02

制造工艺

1.HBM制造工艺包括TSV、Bumping和堆叠等工艺环节

HBM是由多个DRAMdie堆叠而成,利用硅通孔(TSV)和微凸块(Microbump)将die之间相连接,多层DRAMdie再与最下层的Basedie连接,然后通过凸块(Bump)与硅中阶层(interposer)互联。HBM与GPU、CPU或ASIC共同铺设在硅中阶层上,通过CoWoS等2.5D封装工艺相互连接,硅中介层通过CuBump连接至封装基板(Package Substrate)上,最后封装基板再通过锡球与下方的PCB基板相连。

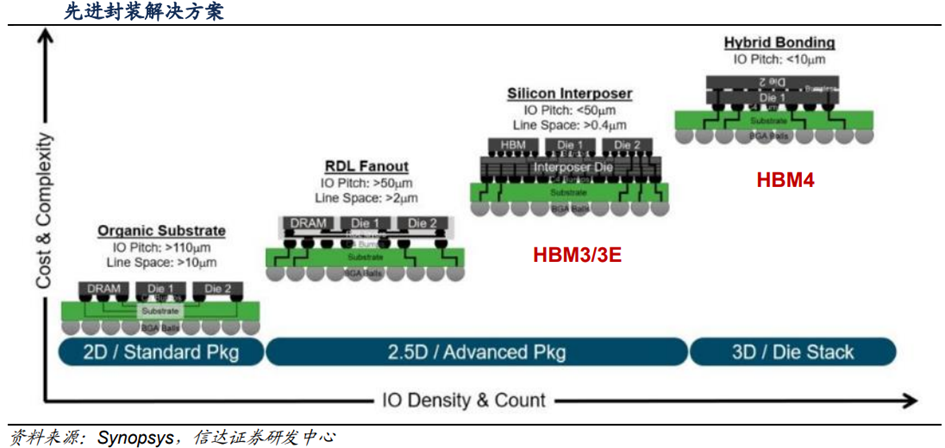

2.存储大厂高度聚焦先进封装,HBM4或将直接放置在处理器上

根据全球半导体观察,目前HBM存储芯片的整体良率在65%左右,HBM良率的高低主要受到其堆叠架构复杂性的影响,这涉及到多层次的内存结构和作为各层连接之用的直通TSV技术。这些复杂技术增加了制程缺陷的风险,可能导致良率低于设计较简单的内存产品。因此存储大厂纷纷加码HBM先进封装,提升HBM良率并降低功耗。此外,根据CFM,SK海力士拟将新一代HBM4堆栈直接放置在处理器上,通过3D堆叠的形式进一步提高I/O数量。

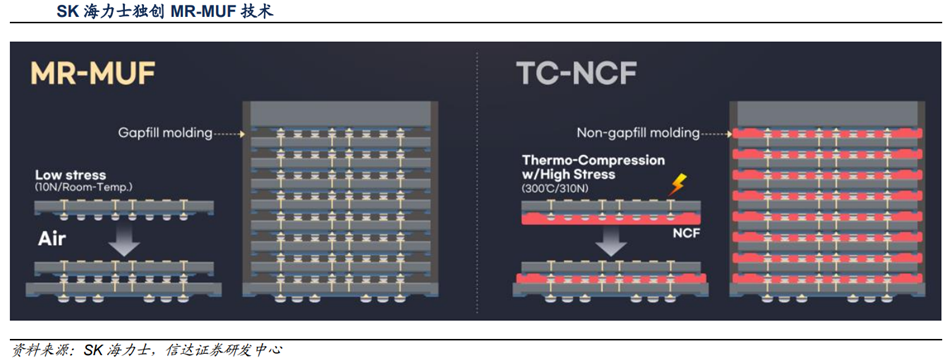

3.SK海力士凭借MR-MUF技术占据HBM市场份额,三星考虑将MUF用于3DSRDIMM

SK海力士在HBM2E和HBM3的生产中引入了大规模回流成型底部填充(MR-MUF)工艺,提高了HBM超过10万个微凸块互连的质量,此外,该工艺充分增加了热虚拟凸块的数量,同时由于采用了高导热率的模制底部填充(MUF)材料,因此散热性能更加出色。根据全球半导体观察,三星认为MUF非常适合3DSRDIMM,而目前3DSRDIMM使用TSV技术制造,主要应用于服务器上,三星正在考虑在其下一代DRAM中MUF技术。若三星也导入MUF,相关制造材料或将持续受益。

03

发展现状

1.国际

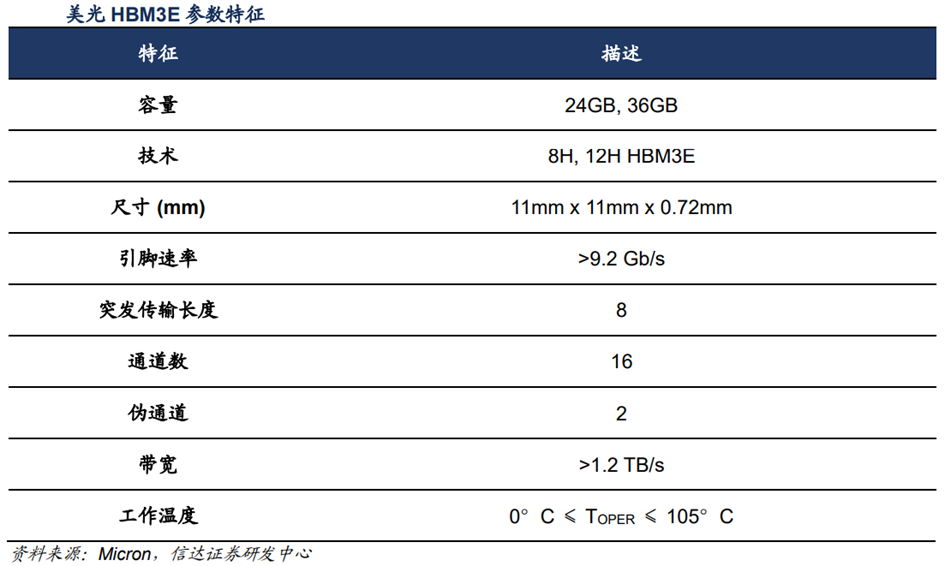

近日,美光宣布已开始量产其HBM3E高带宽内存解决方案。英伟达H200TensorCoreGPU将采用美光8层堆叠的24GB容量HBM3E内存,并于2024年第二季度开始出货。美光HBM3E引脚速率超过9.2Gb/s,提供超过1.2TB/s的内存带宽。与HBM3相比,HBM3E将数据传输速率和峰值内存带宽提高了44%,这对于英伟达H200等需要大量带宽的处理器来说尤其重要。美光利用其1β(1-beta)技术、先进的硅通孔(TSV)和其他实现差异化封装解决方案来生产HBM3E产品,有助于公司在数据中心级产品上提升技术竞争实力和市场占有率。

三星发布首款36GB HBM3E 12HDRAM,目前为三星容量最大的HBM。三星HBM3E12H支持全天候最高带宽达1280GB/s,产品容量也达到了36GB。相比三星8层堆叠的HBM38H,HBM3E12H在带宽和容量上大幅提升超过50%。HBM3E12H采用了先进的热压非导电薄膜(TCNCF)技术,使得12层和8层堆叠产品的高度保持一致,以满足当前HBM封装的要求。相比HBM38H,HBM3E12H搭载于人工智能应用后,公司预计人工智能训练平均速度可提升34%,同时推理服务用户数量也可增加超过11.5倍。

SK海力士率先量产HBM3E,HBM4或于2026年推出。根据半导体行业观察,SK海力士于1月中旬正式结束了HBM3E的开发工作,并顺利完成英伟达历时半年的性能评估,计划于3月开始大规模生产HBM3E产品,这批HBM3E将用于英伟达下一代Blackwell系列的AI芯片旗舰产品B100上,而英伟达则计划于2024年第二季度末或第三季度初推出该系列产品。根据TrendForce,HBM4预计规划于2026年推出,或采取HBM堆栈在SoC主芯片之上的封装方式。

2.国内

国内存储厂商入局HBM市场。根据采招网,近日,武汉新芯发布《高带宽存储芯粒先进封装技术研发和产线建设》招标项目,利用三维集成多晶圆堆叠技术,打造更高容量、更大带宽、更小功耗和更高生产效率的国产高带宽存储器(HBM)产品,推进多晶圆堆叠工艺产业化,新增生产设备约17台/套,拟实现月产出能力≥3000片(12英寸)。国内存储厂商在HBM技术上的加速突破,有望在AI大浪潮的需求下提升竞争实力,相关产业链也或将受益。

04

竞争格局

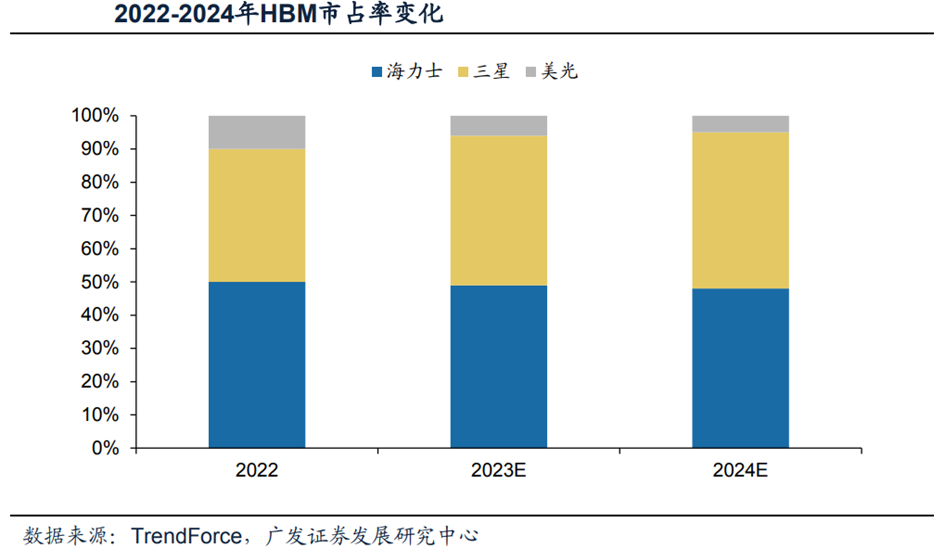

1.寡头垄断,SK海力士占过半份额

HBM市场格局集中,SK海力士占有主导地位。根据Trendforce数据,2023年SK海力士市占率预计为53%,三星市占率38%、美光市占率9%。。

HBM市场竞争白热化。2023年市场主要HBM代际是HBM2、HBM2e和HBM3,算力卡性能提升刺激HBM产品更迭,2023年下半年伴随NVIDIAH100与AMDMI300的搭载,HBM3渗透率提升。2024年伊始,SK海力士完成HBM3e开发,并送样英伟达测试,有望于上半年量产。预计三星电子和美光科技即将送样HBM3e,也有望于上半年量产,其中美光科技跳过了HBM3,直接研发HBM3e。三家原厂在HBM领域的竞争日趋白热化。

2.更多DRAM厂商正切入HBM赛道,国产HBM有望突破

二线、三线DRAM厂商也正在切入HBM赛道。华邦电于2023年8月介绍了其类HBM高带宽产品CUBEx,采用1~4层TSVDRAM堆叠,I/O速度500M~2Gbps,总带宽最高可达1024GB/s,颗粒容量为0.5~4GB,功耗低至不足1pJ/bit。这种比常规HBM拥有更高带宽的CUBEx可用于AR、VR、可穿戴等领域。

国产DRAM厂商有望突破HBM。目前一线厂商DRAM制程在1alpha、1beta水平,国产DRAM制程在25~17nm水平,中国台湾DRAM制程在25~19nm水平,国内DRAM制程接近海外。且国内拥有先进封装技术资源和GPU客户资源,有强烈的国产化诉求,未来国产DRAM厂商有望突破HBM。

05

市场测算

1.AI刺激服务器存储容量扩充,HBM需求强劲

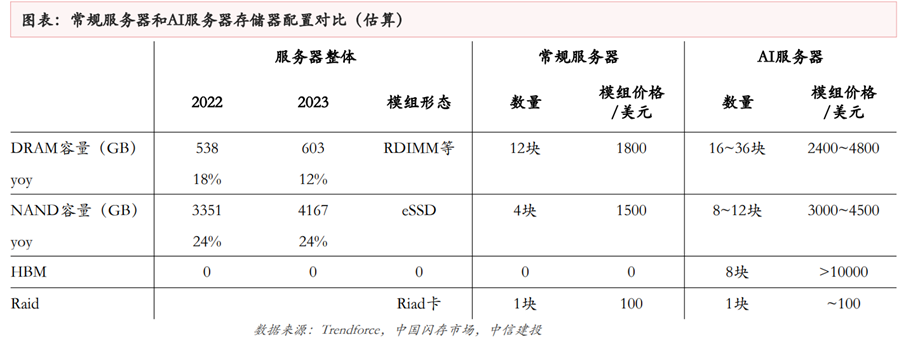

(1)AI服务器刺激更多存储器用量,大容量内存条、HBM、eSSD需求旺盛

根据Trendforce,目前服务器DRAM(模组形态为常规内存条RDIMM和LRDIMM)的普遍配置约为500~600GB,而AI服务器在单条模组上则多采64~128GB,单台服务器搭载16~36条,平均容量可达1TB以上。对于企业级SSD,由于AI服务器追求的速度更高,其要求优先满足DRAM或HBM需求,在SSD的容量提升上则呈现非必要扩大容量的态势,但配置也显著高于常规服务器。

(2)随着算力卡更新迭代,HBM规格持续提升

未来在AI模型逐渐复杂化的趋势下,服务器的数据计算和存储需求将快速增长,并同步带动服务器DRAM、企业级SSD以及HBM的需求成长。相较于一般服务器而言,AI服务器多增加GPGPU的使用,以NVIDIAA100/H10080GB配置8张计算,HBM用量约为640GB,超越常规服务器的内存条容量,H200、B100、MI300等算力卡将搭载更高容量、更高速率HBM。

2.通用服务器呈现弱复苏态势,AI服务器快速增长

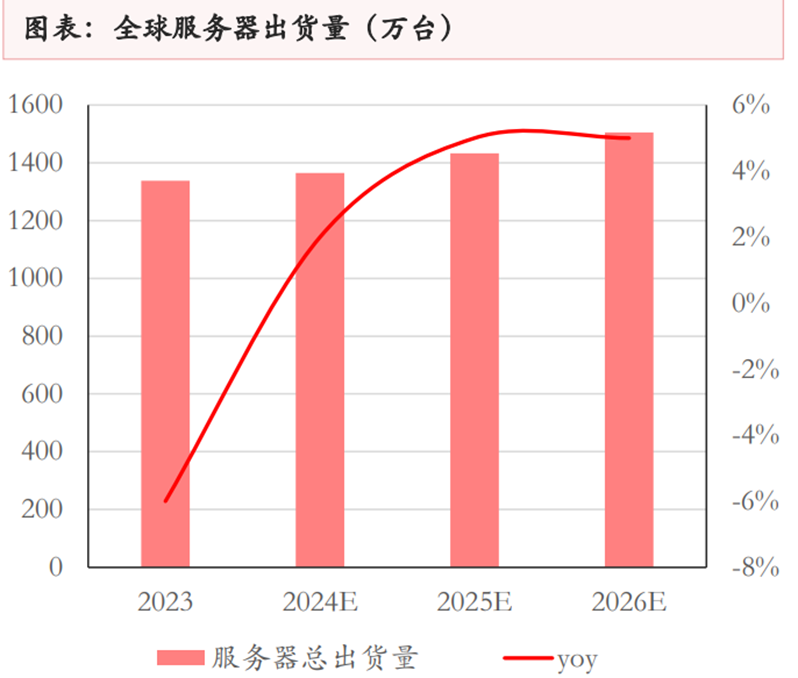

(1)传统服务器呈现弱复苏态势,2024年出货量同比增长2%

根据Trendforce,2024年服务器出货驱动力以北美CSP为主,但受限于通货膨胀高,企业融资成本居高不下,压缩资本支出,整体需求尚未恢复至疫情前成长幅度,预计2024年全球服务器整机出货量约1365.4万台,同比增长2.05%。

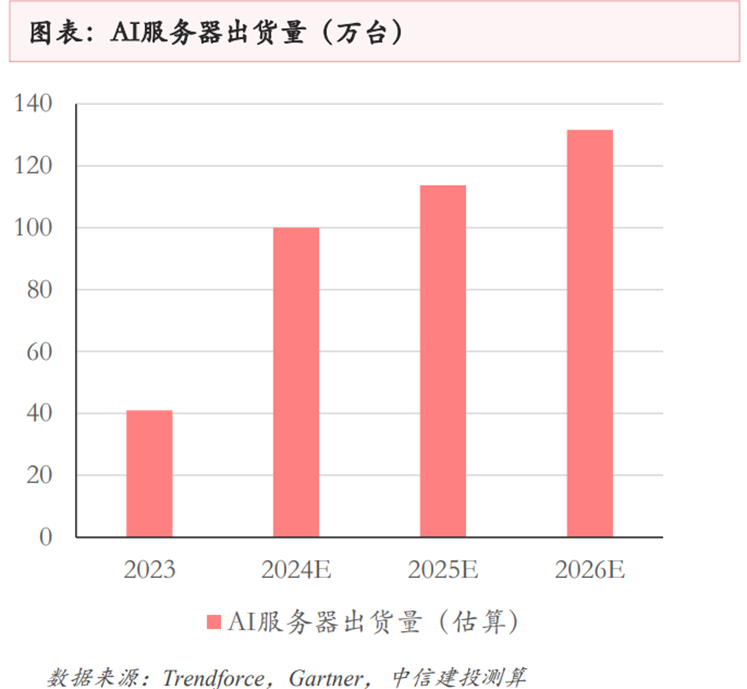

(2)受益于北美CSP订单带动,AI服务器ODM对2024年展望乐观

1)广达:预计2024年AI服务器出货双位数增长,订单主要来自于Microsoft及AWS等;2)Supermicro:预计2024年AI服务器出货量有机会翻倍成长,订单主要来自CoreWeave与Tesla,积极拓展Apple、Meta等客户AI订单;3)Inventec:除了北美CSP需求,中国客户如ByteDance需求最强,预估2024年AI服务器出货量年成长可达双位数,占比约10~15%;4)Foxconn:获得Oracle、AWS订单,预计2024年服务器ODM出货量增长5~7%。

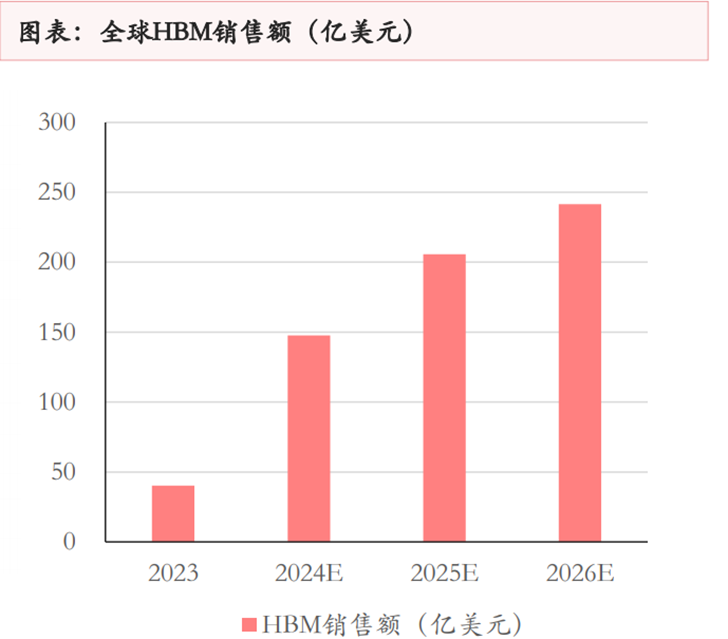

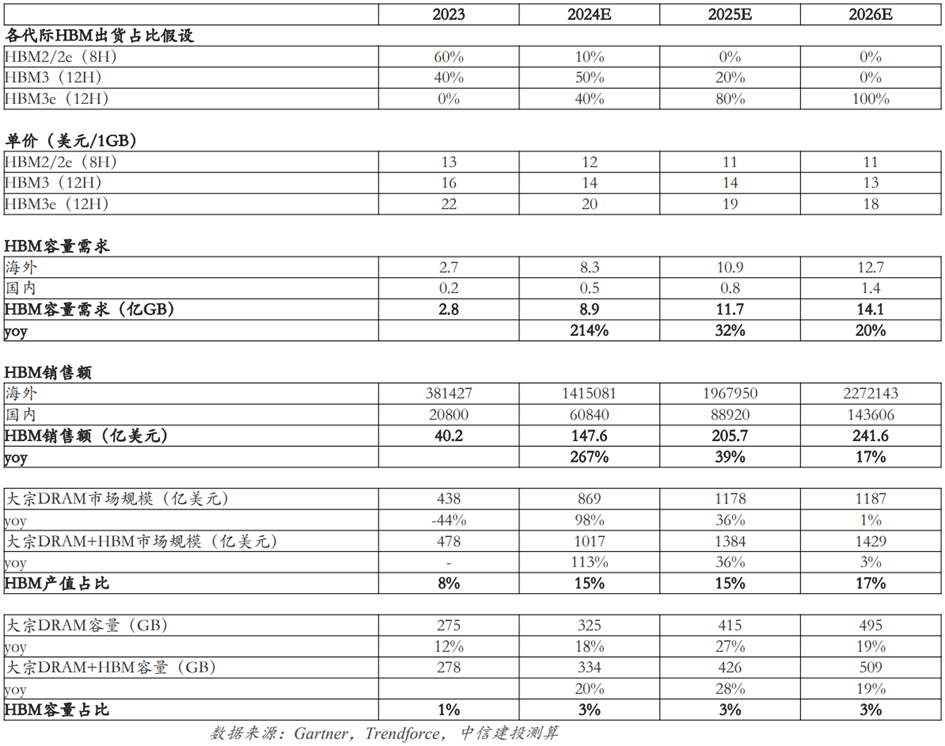

3.2024年HBM市场容量有望接近9亿GB

通过测算全球算力卡的HBM需求,结论是:

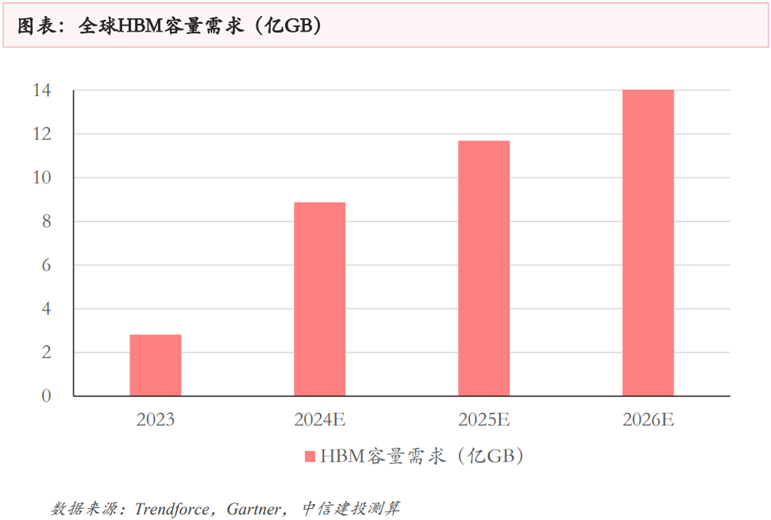

(1)从容量看

2023年HBM市场容量为2.8亿GB,预计2024年增长至8.9亿GB,2026年增长至14.1亿GB,2023~2026年CAGR为71%。增长驱动因素是:算力卡单卡HBM容量提升、算力卡出货量提升、新的玩家产品放量。

AI服务器出货增速远高于传统服务器、手机、PC+NB等传统市场,且单机DRAM容量增速更快,因此HBM在全球DRAM市场的占比将逐步提升,2023年容量占比为1%(2023年大宗DRAM市场容量为275亿GB),2026年将提升至3%。

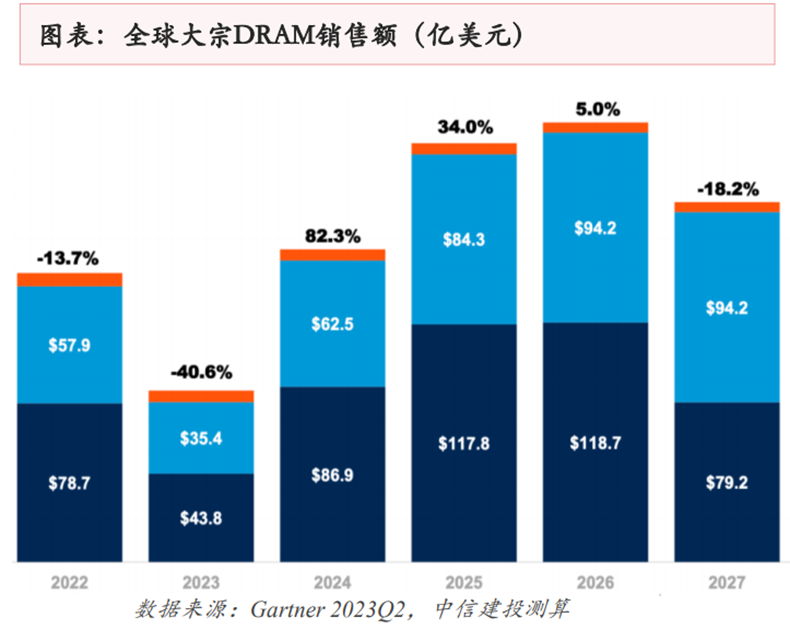

(2)从产值看

2023年HBM市场规模为40亿美元,预计2024年增长至148亿美元,2026年增长至242亿美元,2023~2026年CAGR为82%。增长驱动因素是:算力卡单卡HBM容量提升、算力卡出货量提升、新的玩家产品放量、技术迭代带来单GBHBM单价提升。

大宗DRAM具备强商品属性,价格周期性明显,HBM具备定制品属性,技术迭代催动ASP提升,长期看HBM在DRAM市场的占比会持续提升,2023年HBM销售额在DRAM市场的占比为8%,2026年将提升至17%。

4.HBM市场测算明细及关键假设

关键假设:1)对2025年之后的算力卡增长采用保守假设:2023-2024年算力卡维持紧缺,假设2025年供需平衡,增长趋缓。2)HBM渗透率假设:2023年HBM市场的主流代际为HBM2、HBM2e和HBM3,预计2024年主流代际转变为HBM3e,由于各家原厂的HBM4方案未定,2025~2026年保守假设以HBM3e为主。3)HBM价格假设:定价上HBM3e>HBM3 >HBM2e >HBM2,并且随着产品迭代,老产品价格有自然年降。其中HBM3e有24GB和36GB版本,以24GB版本测算。4)大宗DRAM的容量和销售额来自Gartner预测,包含了2024~2025年的涨价周期和2026年周期顶部的假设,数据中不含HBM。

06

相关公司

1.通富微电

2.中微公司

3.拓荆科技

4.芯源微

5.其他相关公司

07

HBM4

HBM4可看做是HBM技术一个新的分水岭,一方面是HBM领域先进封装技术获得长足发展,更为重要的是产业链出现三大方面的改变。其一,主要内存制造商正计划对高带宽内存技术进行更实质性的改变,一改往常的1024位接口,从更宽的2048位内存接口开始。其二,行业生态改变,三大存储原厂SK海力士、三星、美光与台积电展开高度紧密合作。毕竟在此之前,三家原厂的芯片基本基于本公司自己的制程工艺开展芯片生产。其三,HBM芯片的定制化趋势更为明显。

几家大厂HBM4进度几何?

2024年4月19日,SK海力士宣布,公司就下一代HBM产品生产和加强整合HBM与逻辑层的先进封装技术,将与台积电公司密切合作,双方近期签署了谅解备忘录(MOU)。5月2日,SK海力士在韩国举行的记者招待会上表示,其HBM4量产时间从2026年提至2025年。具体来说,SK海力士计划在2025年下半年推出采用12层DRAM堆叠的首批HBM4产品,而16层堆叠HBM稍晚于2026年推出。因为当前距离量产时间还较早,还没有相关产品参数出来。

SK海力士在HBM方面一直处于领先地位,由其主导并采用的HBM以硅通孔技术(TSV:Through Silicon Via)、批量回流模制底部填充(MR-MUF:Mass Reflow-Molded Underfill)先进封装技术在行业享有盛名。目前随着HBM芯片堆叠层数的增加,MR-MUF技术容易翘曲、导致晶圆末端弯曲、空洞现象(即保护材料在某些区域分布不均匀)的问题引起行业高度关注。SK海力士方表示,正在推进TSV和MR-MUF的技术发展。与HBM开发初期相比,他们成功地减少了翘曲现象,目前正在开发克服这一问题的技术。下一步,抉择会聚焦在减少空隙。

此外,SK海力士还致力于芯粒(Chiplet)及混合键合(Hybrid bonding)等下一代先进封装技术的开发,以支持半导体存储器和逻辑芯片之间的异构集成,同时促进新型半导体的发展。当中,Hybrid bonding也是被看作是HBM封装的又一个新选择。但根据之前的计划不一样,SK海力士打算在下一代的HBM 4中持续采用尖端封装技术MR-MUF。作为替代方案而出现的混合键合技术预计由于HBM标准的放宽而缓慢引入。

三星方面则计划通过针对高温环境优化的NCF组装技术和尖端工艺技术,将16H技术融入下一代HBM4中。据三星的规划,HBM 4将在2025年生产样品。另外据外媒报道,三星在早前的一个会议上表示,正在考虑在HBM 4中使用混合键合或NCF。其认为,混合键合更具优势,因为它们可以紧凑地添加更多堆叠,而无需使用填充凸块进行连接的硅通孔(TSV)。使用相同的技术,HBM上的核心芯片DRAM也可以变得更厚。

这里值得关注的便是三星在HBM封装上采用的TC-NCF非导电薄膜热压缩先进封装技术。这是一种与SK海力士MR-MUF略有不同的技术。在每次堆叠芯片时,都会在各层之间放置一层不导电的粘合膜。该薄膜是一种聚合物材料,用于使芯片彼此绝缘并保护连接点免受撞击。随着发展,三星逐渐减少了NCF材料的厚度,将12层第五代HBM3E的厚度降至7微米(μm)。该公司认为这种方法的优点是可以最大限度地减少随着层数增加和芯片厚度减小而可能发生的翘曲,使其更适合构建更高的堆栈。

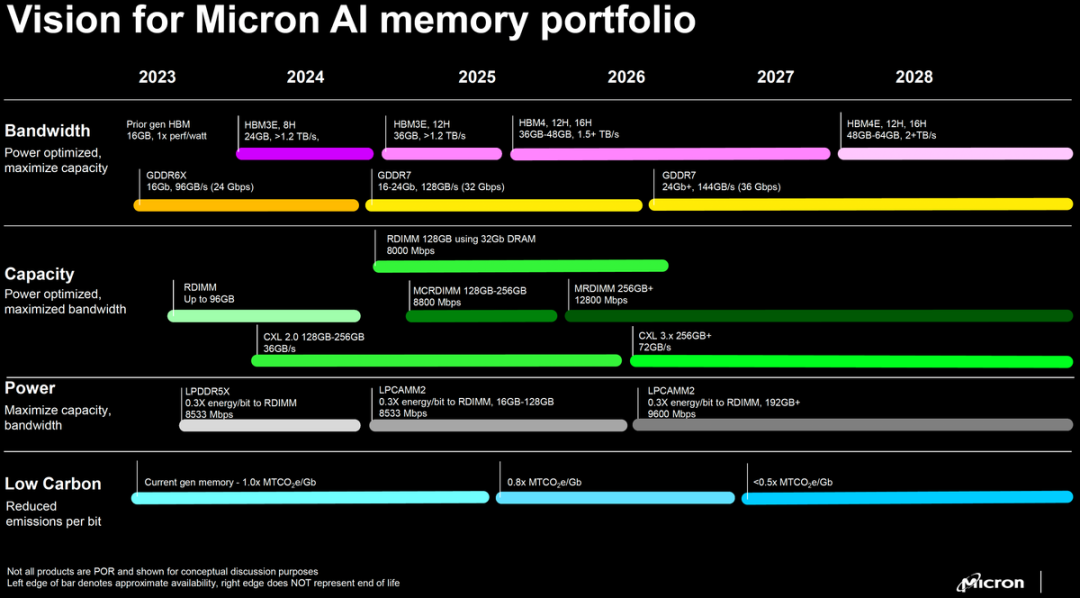

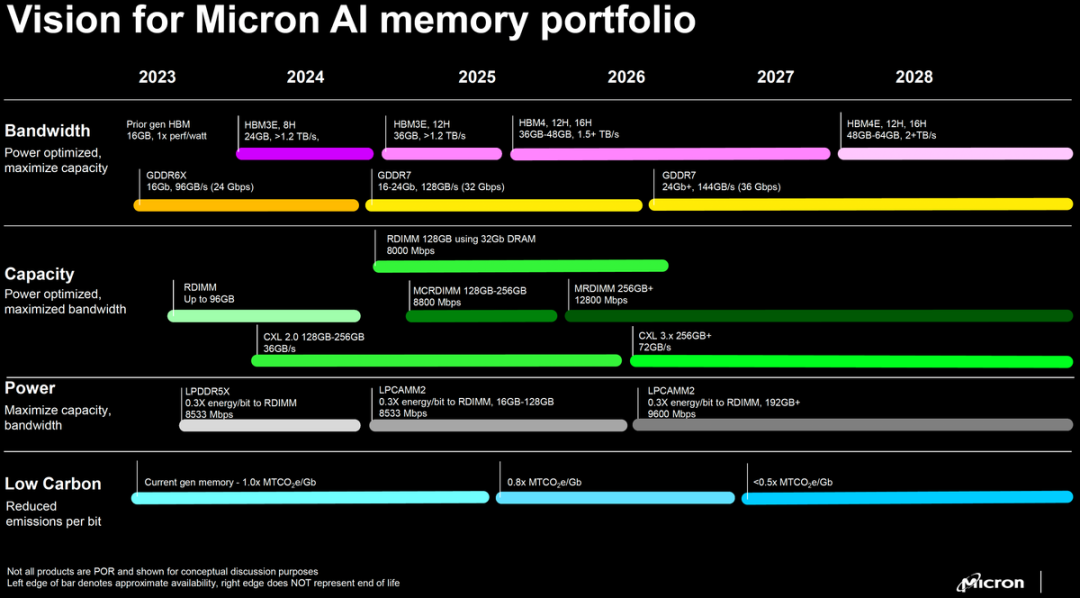

美光是这场HBM战局中的半路杀出者,毕竟它一入局,便将目光投向了HBM3。如下图所示,美光晒出了其HBM3E和HBM4产品路线图。方案路线图显示,其HBM4预计在2026年推出,而到2028年则由HBM4E接棒。

图片来源:美光

关于未来的布局,美光披露了暂名为HBMnext的下一代HBM内存,业界猜测这有可能便是其HBM 4。美光预计HBMNext将提供36 GB和64 GB容量,这意味着多种配置,例如12-Hi 24 Gb堆栈(36 GB)或16-Hi 32 Gb堆栈(64 GB)。至于性能,美光宣称每个堆栈的带宽为1.5 TB/s–2+TB/s,这意味着数据传输速率超过11.5 GT/s/pin。

2024年4月19日,SK海力士宣布,公司就下一代HBM产品生产和加强整合HBM与逻辑层的先进封装技术,将与台积电公司密切合作,双方近期签署了谅解备忘录(MOU)。5月2日,SK海力士在韩国举行的记者招待会上表示,其HBM4量产时间从2026年提至2025年。具体来说,SK海力士计划在2025年下半年推出采用12层DRAM堆叠的首批HBM4产品,而16层堆叠HBM稍晚于2026年推出。因为当前距离量产时间还较早,还没有相关产品参数出来。

SK海力士在HBM方面一直处于领先地位,由其主导并采用的HBM以硅通孔技术(TSV:Through Silicon Via)、批量回流模制底部填充(MR-MUF:Mass Reflow-Molded Underfill)先进封装技术在行业享有盛名。目前随着HBM芯片堆叠层数的增加,MR-MUF技术容易翘曲、导致晶圆末端弯曲、空洞现象(即保护材料在某些区域分布不均匀)的问题引起行业高度关注。SK海力士方表示,正在推进TSV和MR-MUF的技术发展。与HBM开发初期相比,他们成功地减少了翘曲现象,目前正在开发克服这一问题的技术。下一步,抉择会聚焦在减少空隙。

此外,SK海力士还致力于芯粒(Chiplet)及混合键合(Hybrid bonding)等下一代先进封装技术的开发,以支持半导体存储器和逻辑芯片之间的异构集成,同时促进新型半导体的发展。当中,Hybrid bonding也是被看作是HBM封装的又一个新选择。但根据之前的计划不一样,SK海力士打算在下一代的HBM 4中持续采用尖端封装技术MR-MUF。作为替代方案而出现的混合键合技术预计由于HBM标准的放宽而缓慢引入。

三星方面则计划通过针对高温环境优化的NCF组装技术和尖端工艺技术,将16H技术融入下一代HBM4中。据三星的规划,HBM 4将在2025年生产样品。另外据外媒报道,三星在早前的一个会议上表示,正在考虑在HBM 4中使用混合键合或NCF。其认为,混合键合更具优势,因为它们可以紧凑地添加更多堆叠,而无需使用填充凸块进行连接的硅通孔(TSV)。使用相同的技术,HBM上的核心芯片DRAM也可以变得更厚。

这里值得关注的便是三星在HBM封装上采用的TC-NCF非导电薄膜热压缩先进封装技术。这是一种与SK海力士MR-MUF略有不同的技术。在每次堆叠芯片时,都会在各层之间放置一层不导电的粘合膜。该薄膜是一种聚合物材料,用于使芯片彼此绝缘并保护连接点免受撞击。随着发展,三星逐渐减少了NCF材料的厚度,将12层第五代HBM3E的厚度降至7微米(μm)。该公司认为这种方法的优点是可以最大限度地减少随着层数增加和芯片厚度减小而可能发生的翘曲,使其更适合构建更高的堆栈。

美光是这场HBM战局中的半路杀出者,毕竟它一入局,便将目光投向了HBM3。如下图所示,美光晒出了其HBM3E和HBM4产品路线图。方案路线图显示,其HBM4预计在2026年推出,而到2028年则由HBM4E接棒。

图片来源:美光

关于未来的布局,美光披露了暂名为HBMnext的下一代HBM内存,业界猜测这有可能便是其HBM 4。美光预计HBMNext将提供36 GB和64 GB容量,这意味着多种配置,例如12-Hi 24 Gb堆栈(36 GB)或16-Hi 32 Gb堆栈(64 GB)。至于性能,美光宣称每个堆栈的带宽为1.5 TB/s–2+TB/s,这意味着数据传输速率超过11.5 GT/s/pin。

谈谈HBM4以后的专业化、定制化趋势

在谈及HBM4时,台积电以及SK海力士、三星、美光均提及专业定制化趋势。据悉,目前三大原厂目前与英伟达、AMD、微软签订的HBM供应协议早已开启了定制条款。

SK海力士认为,市场将更倾向于专业化(Specialized)和定制化(Customized)产品,以满足客户需求。他强调,对于新一代HBM,卓越的性能是基本条件,同时,还须具备满足不同客户的特定需求、超越传统存储器性能的优势。

三星则表示,业界越来越认识到,处理器和内存公司各自优化其产品的孤立努力不足以释放AGI时代所需的创新。因此,“定制HBM”成为潮流,这也代表了实现处理器和内存之间协同优化以加速这一趋势的第一步。为此,三星利用其在内存、代工、系统LSI和先进封装方面的综合能力。

在刚刚结束的美光科技交流会上,美光透露出一条重磅消息,在HBM产能不足的背景下,业内已经越来越倾向于定制化的HBM产品,主要是因为下游客户越发个性化的需求。为了解决客户对于性能、功能、尺寸、形态、功效等方面的差异化需求,市场将更倾向于打造专业化(Specialized)和定制化(Customized)HBM产品。

此前,行业针对HBM大规模扩产的行为产生未来是否会过剩担忧。行业人士表示,专业化和定制化可以有效解决这类问题。由于定制化的存储产品与客户需求高度耦合,未来存储厂商和客户会有更深的绑定关系。这一改变可以增加HBM下游供给的确定性,使得存储厂商在做产能规划的时候更有计划性。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。